- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄67968 > MJ80C52XXX-36 (ATMEL CORP) 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | MJ80C52XXX-36 |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| 封裝: | JLCC-44 |

| 文件頁(yè)數(shù): | 18/20頁(yè) |

| 文件大小: | 194K |

| 代理商: | MJ80C52XXX-36 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)

80C32/80C52/80C32E

7

Rev. J

– July 03, 2000

5.1. Idle Mode

The instruction that sets PCON.0 is the last instruction executed before the Idle mode is activated. Once in the Idle

mode the CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word,

Accumulator, RAM and all other registers maintain their data during idle. Table 1. describes the status of the external

pins during Idle mode.

There are three ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared

by hardware, terminating Idle mode. The interrupt is serviced, and following RETI, the next instruction to be executed

will be the one following the instruction that wrote 1 to PCON.0.

The flag bits GF0 and GF1 may be used to determine whether the interrupt was received during normal execution or

during the Idle mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits.

When Idle mode is terminated by an enabled interrupt, the service routine can examine the status of the flag bits.

The second way of terminating the Idle mode is with a hardware reset. Since the oscillator is still running, the hardware

reset needs to be active for only 2 machine cycles (24 oscillator periods) to complete the reset operation.

5.2. Power Down Mode

The instruction that sets PCON.1 is the last executed prior to entering power down. Once in power down, the oscillator

is stopped. The contents of the onchip RAM and the Special Function Register is saved during power down mode. The

hardware reset initiates the Special Fucntion Register. In the Power Down mode, VCC may be lowered to minimize

circuit power consumption. Care must be taken to ensure the voltage is not reduced until the power down mode is

entered, and that the voltage is restored before the hardware reset is applied which freezes the oscillator. Reset should

not be released until the oscillator has restarted and stabilized.

Table 1. describes the status of the external pins while in the power down mode. It should be noted that if the power

down mode is activated while in external program memory, the port data that is held in the Special Function Register

P2 is restored to Port 2. If the data is a 1, the port pin is held high during the power down mode by the strong pullup,

T1, shown in Figure 4.

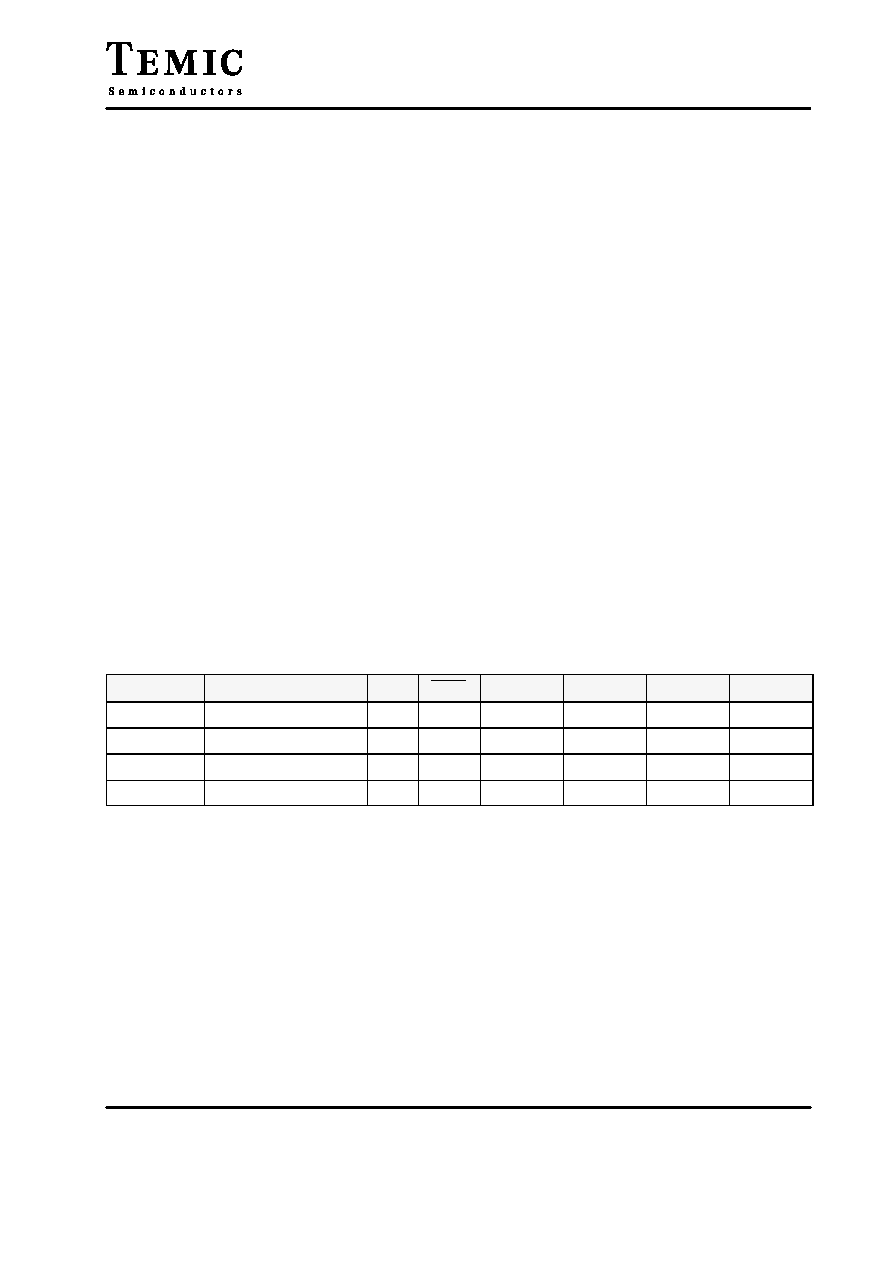

Table 1. Status of the external pins during idle and power down modes

Mode

Program Memory

Ale

PSEN

PORT0

PORT1

PORT2

PORT3

Idle

Internal

1

Port Data

Idle

External

1

Floating

Port Data

Address

Port Data

Power Down

Internal

0

Port Data

Power Down

External

0

Floating

Port Data

5.3. Stop Clock Mode

Due to static design, the TEMIC 80C32/C52 clock speed can be reduced until 0 MHz without any data loss in memory

or registers. This mode allows step by step utilization, and permits to reduce system power consumption by bringing

the clock frequency down to any value. At 0 MHz, the power consumption is the same as in the Power Down Mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD80C32EXXX-30MQ | 8-BIT, 30 MHz, MICROCONTROLLER, CDIP40 |

| MC80C32XXX-12/883 | 8-BIT, 12 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52XXX-36 | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CDIP40 |

| MJ80C32XXX-12MQ | 8-BIT, 12 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52XXX-36/883 | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MJ8100 | 制造商:ASI 功能描述:8100 N11E4C |

| MJ8100R | 制造商:SEME-LAB 制造商全稱:Seme LAB 功能描述:Bipolar PNP Device in a Hermetically sealed TO39 |

| MJ-82-1 | 制造商:SPC Multicomp 功能描述:SOCKET PCB DC POWER 制造商:SPC Multicomp 功能描述:SOCKET, PCB, DC POWER 制造商:SPC Multicomp 功能描述:SOCKET, PCB, DC POWER; Gender:Receptacle; Connector Mounting:PCB; Contact Termination:Through Hole Vertical; Connector Mounting Orientation:PCB; Connector Type:Standard Power Entry ;RoHS Compliant: Yes |

| MJ8250FE | 制造商:Ohmite Mfg Co 功能描述: |

| MJ8251F | 制造商:Ohmite Mfg Co 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。