- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25635 > MD80C52TXXX-16SHXXX:D (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | MD80C52TXXX-16SHXXX:D |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| 文件頁數(shù): | 64/125頁 |

| 文件大?。?/td> | 6456K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁當(dāng)前第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁

230

32117D–AVR-01/12

AT32UC3C

14.6.2

Event Shaper (EVS) Operation

PEVC contains Event Shapers (EVS) for certain types of generators:

Asynchronous generators and/or external input

General-purpose waveforms like timer outputs or Generic Clocks

Each Event Shaper is responsible of shaping one input, prior to going through a PEVC channel:

Synchronize asynchronous external inputs

Apply any additional glich-filtering

Detect rise, fall, or both edges of the incoming signal

14.6.2.1

Input Glitch Filter (IGF)

Input Glitch Filtering can be turned on or off by writing to the Input Glitch Filter (IGF) field of the

corresponding Event Shaper Register (EVS).

When IGF is on, the incoming event is sampled periodically. The sampling clock is divided from

CLK_RCSYS by the value of the Input Glitch Filter Divider Register (IGFDR). IGF will filter out

spikes and propagate only incoming events that respect one of the following two conditions :

rise event : 2 samples low, followed by 0+ changes, followed by 2 samples high

fall event : 2 samples high, followed by 0+ changes, followed by 2 samples low

Both CLK_RCSYS and CLK_PEVC must be enabled to use Input Glitch Filtering.

14.6.3

Event Propagation Latency

Once a channel is setup, incoming peripheral events are relayed by hardware. Event progation

latency is therefore cycle deterministic. However, its value depends on the exact settings that

apply to a given channel.

When the channel multiplexer CHMXn.EVMX selects a generator without Event Shaper, event

propagation latency is 0 cycle. Software event is a particular case of 0 cycle propagation.

When the channel multiplexer CHMXn.EVMX selects a generator with Event Shaper, event

propagation latency depends on Input Glitch Filter setting EVSm.IGF :

IGF off : event propagation latency is lesser or equal to 2 CLK_PEVC cycles

IGF on : event propagation latency is lesser or equal to 3 * 2IGFDR+1 * CLK_RCSYS cycles

Please refer to the Module Configuration section at the end of this chapter for the list of genera-

tors implementing Event Shapers.

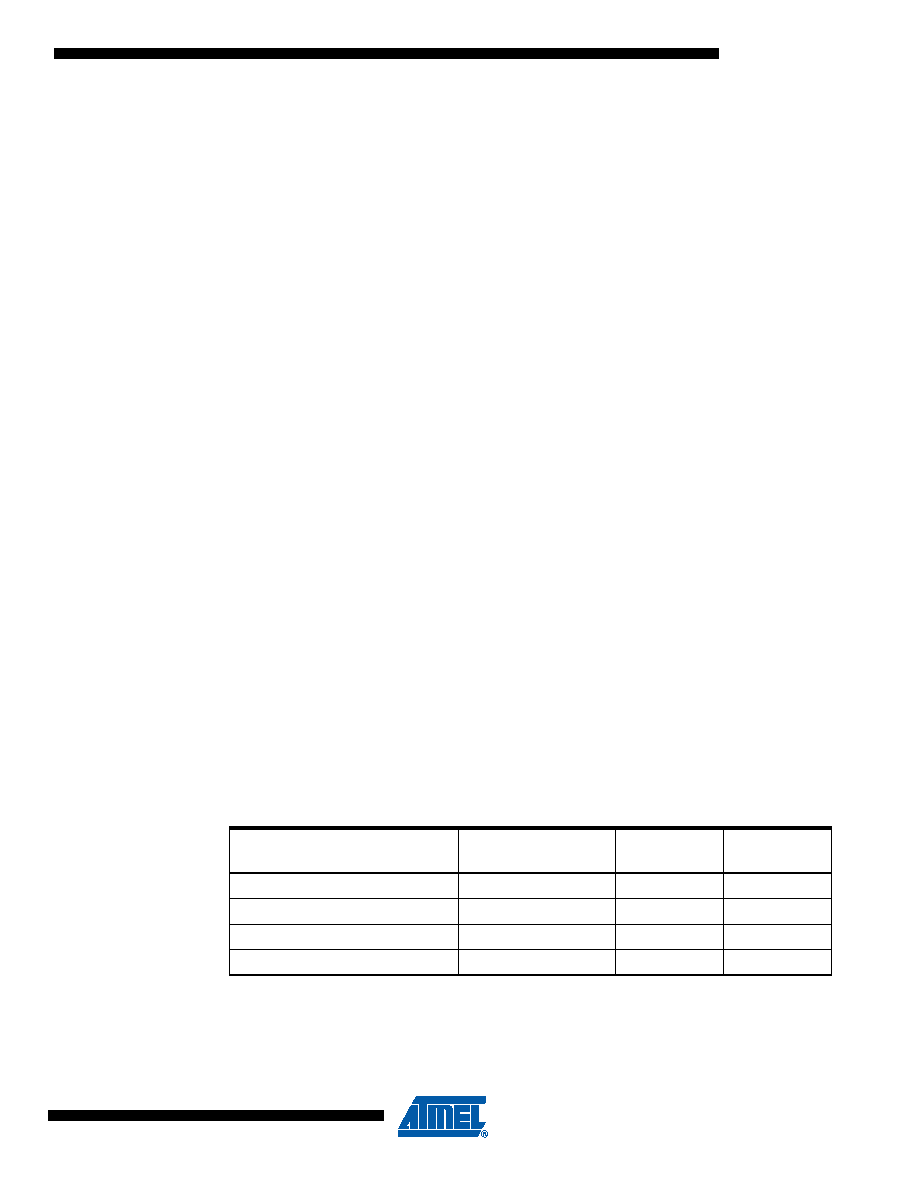

Table 14-2.

Event Propagation Latency

Generator

CHMXn.EVMX

Input Glitch Filter

EVSm.IGF

Latency

Clock

Generator without Event Shaper

-

0

-

Software event

-

0

-

Generator with Event Shaper

Off

2

CLK_PEVC

Generator with Event Shaper

On

3 * 2IGFDR+1

CLK_RCSYS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MR80C52CXXX-12SCR | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C52XXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQFP44 |

| MD80C52EXXX-20SB | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-16SBD | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| MD80C52EXXX-20SB | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MD80C86 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C862 | 制造商:Intel 功能描述:PROCESSOR:MICRO-PROCESSOR |

| MD80C86-2 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CMOS 16-Bit Microprocessor |

| MD80C86-2/883 | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube 制造商:Rochester Electronics LLC 功能描述:CPU 16BILT 5V CMOS 8MHZ 40CDIP - Bulk |

| MD80C86-2/B | 制造商:Intersil Corporation 功能描述:MPU 16BIT CMOS 8MHZ 40CDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。