- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371089 > MCM64PC32T (Motorola, Inc.) 256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium PDF資料下載

參數(shù)資料

| 型號(hào): | MCM64PC32T |

| 廠商: | Motorola, Inc. |

| 英文描述: | 256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| 中文描述: | 256K/512K流水線BurstRAM二級(jí)高速緩存模塊奔騰 |

| 文件頁(yè)數(shù): | 5/16頁(yè) |

| 文件大小: | 167K |

| 代理商: | MCM64PC32T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

MCM64PC32T

MCM64PC64T

5

MOTOROLA FAST SRAM

PIN DESCRIPTIONS

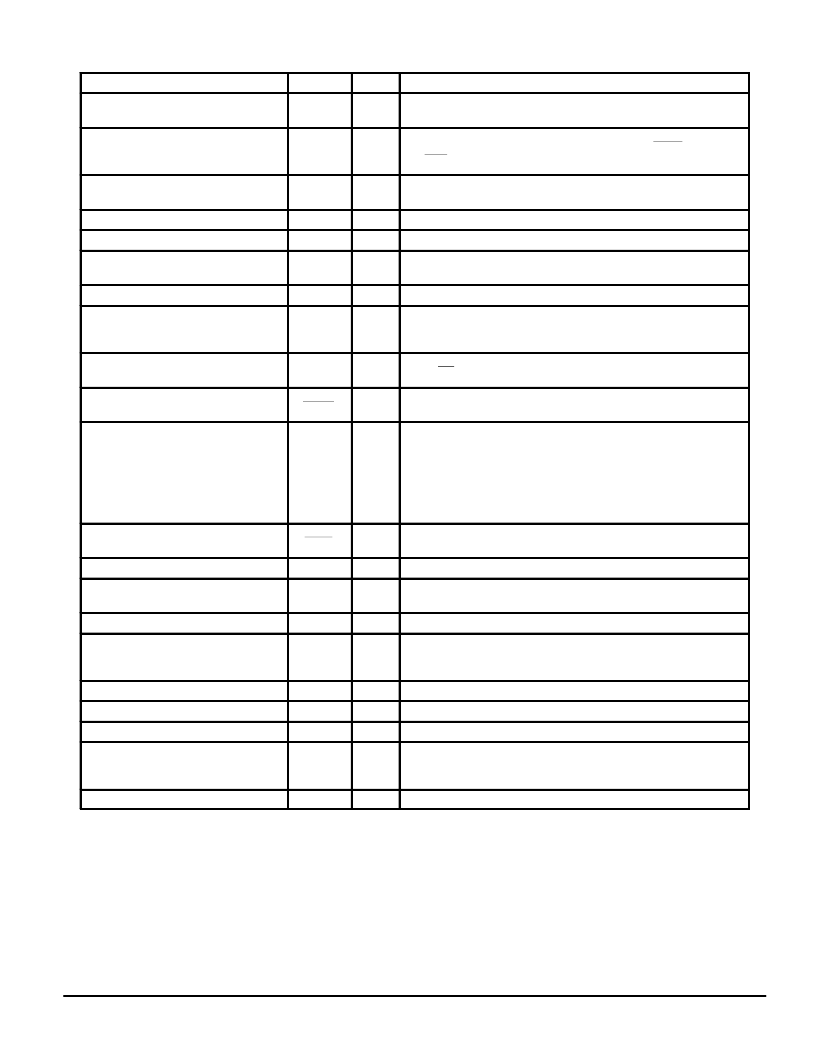

160–Lead Card Edge Pin Locations

Symbol

Type

Description

20, 21, 22, 23, 24, 26, 28, 29,

101, 102, 103, 104, 106, 108, 109, 110

A3 – A18

Input

Address Inputs: These inputs are registered into data RAMs and must

meet setup and hold times. The tag RAM addresses are not registered.

30

ADSP

Input

Address Status Processor: Initiates READ, WRITE, or chip deselect

cycle (Exception–chip deselect does not occur when ADSP is asserted

and CCS is high.

114

BOSEL

Input

Burst Order Select: NC for interleaved burst counter. Tie to ground for

linear burst counter.

18

BWE

Input

Byte Write Enable: To be used in future modules.

9

CADS

Input

Cache Address Status: Initiates READ, WRITE, or chip deselect cycle.

89

CADV

Input

Cache Burst Advance: Increments address count in accordance with

interleaved count style.

16

CCS

Input

Chip Select: Active low chip enable for data RAMs.

91

CG

Input

Cache Output Enable: Active low asynchronous input.

Low–enables output buffers (DQ pins)

High–DQx pins are high impedance.

36, 116

CLK0,

CLK1

Input

Clock: This signal registers the address, data in, and all control signals

except CG.

11, 12, 13, 14, 92, 93, 94, 96

CWE0 –

CWE7

Input

Cache Data Byte Write Enable: Active low write signal for data RAMs.

38, 40, 41, 42, 44, 45, 46, 47, 49, 50, 51,

53, 54, 55, 57, 58, 59, 61, 62, 63, 65, 66,

67, 69, 70, 71, 73, 74, 75, 77, 78, 79,

118, 120, 121, 122, 124, 125, 126, 127,

129, 130, 131, 133, 134, 135, 137, 138,

139, 141, 142, 143, 145, 146, 147, 149,

150, 151, 153, 154, 155, 157, 158, 159

DQ0 –

DQ63

I/O

Synchronous Data I/O:

Drives data out of data RAMs during READ cycles.

Stores data to data RAMs during WRITE cycles.

31, 32

ECS1,

ECS2

Input

Expansion Chip Select

17

GWE

Input

Global Write Enable: To be used in future modules.

33, 34, 112, 113

PD0 –

PD3

—

Presence Detect: See Presence Detect Table

100, 111

RSVD

—

No Connection: Reserved for future use.

2, 3, 4, 5, 82, 83, 84, 85

TIO0 –

TIO7

I/O

Tag RAM I/O:

Drives data out during tag compare cycles.

Stores data to tag RAM during tag WRITE cycles.

8

TWE

Input

Tag Write Enable: Active low write signal for tag RAMs.

7, 15, 25, 39, 52, 60, 68, 76

VDD3

VDD5

VSS

Supply

Power Supply: 3.3 V + 10%, – 5%.

87, 95, 105, 119, 132, 140, 148, 156

Supply

Power Supply: 5.0 V

±

5%.

1, 10, 19, 27, 35, 37, 43, 48, 56, 64, 72,

80, 81, 90, 99, 107, 115, 117, 123, 128,

136, 144, 152, 160

Supply

Ground

6, 86, 88, 97, 98

NC

—

No Connection: There is no connection to the module.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM6706RJ8 | 32K x 8 Bit Static Random Access Memory |

| MCM6706J6 | Circular Connector; Body Material:Aluminum; Series:PT06; Number of Contacts:41; Connector Shell Size:20; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:20-41 |

| MCM6706J7 | Circular Connector; Body Material:Aluminum; Series:PT06; No. of Contacts:41; Connector Shell Size:20; Connecting Termination:Crimp; Circular Shell Style:Straight Plug; Circular Contact Gender:Socket; Insert Arrangement:20-41 |

| MCM6706BRJ8R | 32K x 8 Bit Static Random Access Memory |

| MCM6706ARJ8R2 | 32K x 8 Bit Static Random Access Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCM64PC32TSG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC64SG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PC64TSG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PD32 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

| MCM64PD32SG66 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:256K/512K Pipelined BurstRAM Secondary Cache Module for Pentium |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。