- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69030 > MCAQE32G8APP-0XA FLASH MEMORY DRIVE CONTROLLER, PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | MCAQE32G8APP-0XA |

| 元件分類: | 存儲(chǔ)控制器/管理單元 |

| 英文描述: | FLASH MEMORY DRIVE CONTROLLER, PQFP |

| 封裝: | LQFP |

| 文件頁(yè)數(shù): | 16/62頁(yè) |

| 文件大?。?/td> | 740K |

| 代理商: | MCAQE32G8APP-0XA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)當(dāng)前第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

NAND Flash-based Solid State Disk

23

Nov. 15. 2006

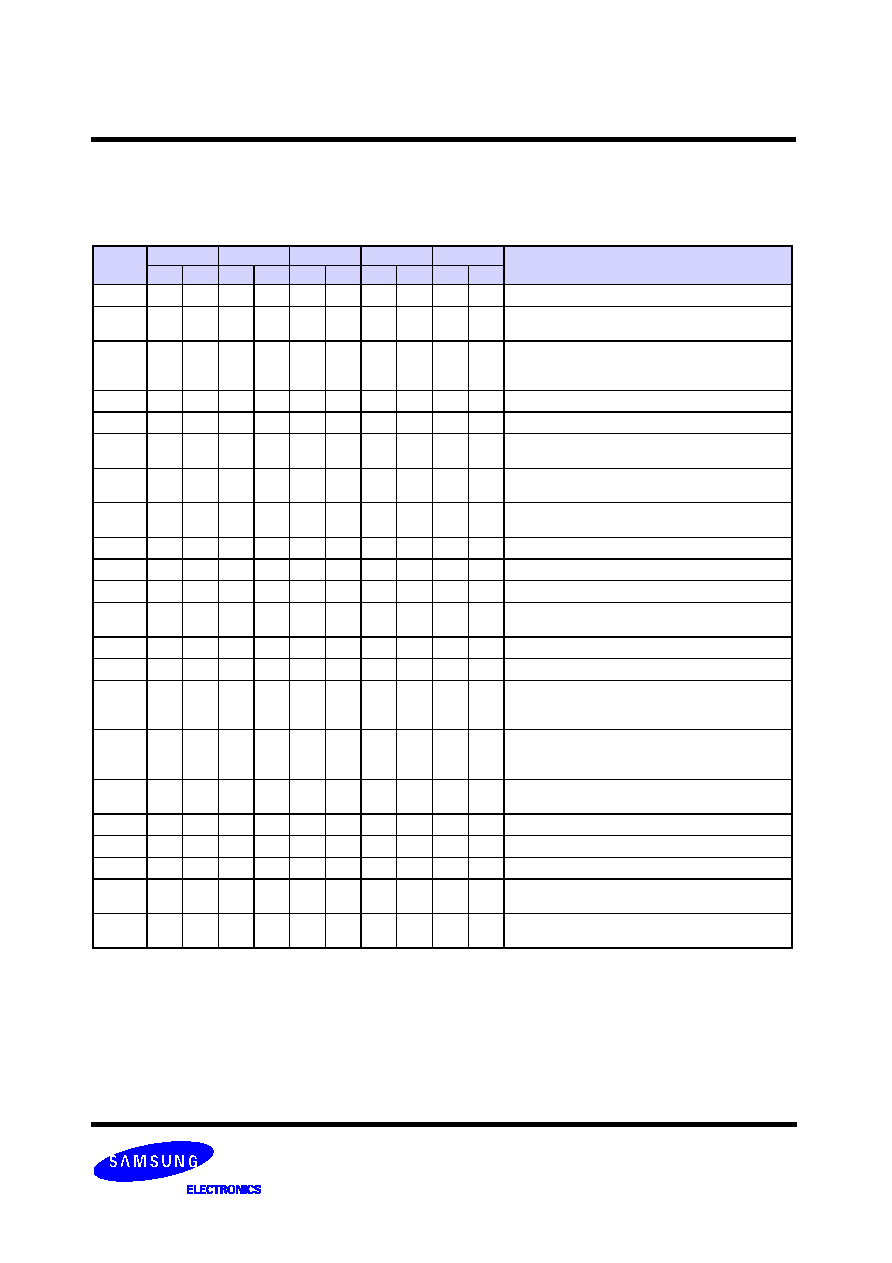

Figure 7 through Figure 16 define the timings associated with all phases of Ultra DMA bursts.

Table 4 contains the values for the timings for each of the Ultra DMA modes.

Table 4 - Ultra DMA data burst timing requirements

NOTE:

1. Timing parameters shall be measured at the connector of the sender or receiver to which the parameter applies. For example, the sender shall stop

generating STROBE edges tRFS after the negation of DMARDY-. Both STROBE and DMARDY- timing measurements are taken at the connector of the

sender.

2. All timing measurement switching points(low to high and high to low) shall be taken at 1.5V.

3. tUI, tMLI, and tLI indicate sender-to-recipient or recipient-to-sender interlocks, i.e., either sender or recipient is waiting for the other to respond with a

signal before proceeding. tUI is an inlimited interlock that has no maximum time value. tMLI is a limited time-out that has a defined minimum. tLI is a lim-

ited time-out that has a defined maximum.

4. The test load for tDVS and tDVH shall be a lumped capacitor load with no cable or receivers. Timing for tDVS and tDVH shall be met for all capacitive

loads from 15 to 40 pf where all signals have the same capacitive load value.

5. tZIORDY may be greater than tENV since the device has a pull up on IORDY- giving it a known state when released.

Name

Mode 0

Mode 1

Mode 2

Mode 3

Mode 4

Comment

(See Notes 1 and 2)

min

max

min

max

min

max

min

max

min

max

t2CYCTYP 240

160

120

90

60

Typical sustained average two cycle time

tCYC

112

7354

3925

Cycle time allowing for asymmetry and clock varia-

tions (from STROBE edge to STROBE edge)

t2CYC

230

154

115

86

57

Two cycle time allowing for clock variations (from ris-

ing edge to next rising edge or from falling edge to

next falling edge of STROBE)

tDS

15

10

7

5

Data setup time at recipient

tDH

5

Data hold time at recipient

tDVS

70

48

30

20

6

Data valid setup time at sender (from data valid until

STROBE edge) (See Note 4)

tDVH

666

66

Data valid hold time at sender (from STROBE edge

until data may become invalid) (See Note 4)

tFS

0

230

0

200

0

170

0

130

0

120

First STROBE time (for device to first negate

DSTROBE from STOP during a data in burst)

tLI

0

150

0

150

0

150

0

100

0

100 Limited interlock time (See Note 3)

tMLI

20

Interlock time with minimum(See Note 3)

tUI

0

Unlimited interlock time (See Note 3)

tAZ

10

Maximum time allowed for output drivers to release

(from asserted or negated)

tZAH

20

Minimum delay time required for output

tZAD

0

Drivers to assert or negate (from released)

tENV

20

70

20

70

20

70

20

55

20

55

Envelope

time

(from

DMACK-

to

STOP

and

HDMARDY- during data in burst initiation and from

DMACK to STOP during data out burst initiation)

tSR

50

30

20

NA

STROBE-to-DMARDY- time (if DMARDY- is negated

before this long after STROBE edge, the recipient

shall receive no more than one additional data word)

tRFS

75

70

60

Ready-to-final-STROBE time (no STROBE edges

shall be sent this long after negation of DMARDY-)

tRP

160

125

100

Minimum time to assert STOP or negate DMARQ

tIORDYZ

20

Maximum time before releasing IORDY

tZIORDY

0

Minimum time before driving STROBE (See Note 5)

tACK

20

Setup and hold times for DMACK- (before assertion

or negation)

tSS

50

Time from STROBE edge to negation of DMARQ or

assertion of STOP (when sender terminates a burst)

4.6.4 Ultra DMA data burst

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC908AZ32AVFU | 8-BIT, FLASH, 8.4 MHz, MICROCONTROLLER, PQFP64 |

| MC908AZ32ACFU | 8-BIT, FLASH, 8.4 MHz, MICROCONTROLLER, PQFP64 |

| MC908AZ32AMFU | 8-BIT, FLASH, 8.4 MHz, MICROCONTROLLER, PQFP64 |

| MC908AZ32AMFUE | 8-BIT, FLASH, 8.4 MHz, MICROCONTROLLER, PQFP64 |

| MC908AZ32AVFU | 8-BIT, FLASH, 8.4 MHz, MICROCONTROLLER, PQFP64 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCAQE32G8APP-0XA00 | 制造商:Samsung SDI 功能描述:Flash Card 32G-byte 3.3V/5V Flash Disk 44-Pin Tray |

| MCAS015.XP | 制造商:Littelfuse 功能描述:FUSE - MCASE 32V 15A 1-PC CARD 制造商:Littelfuse 功能描述:RETAIL / FUSE - MCASE 32V 15A 1-pc Card |

| MCAS020.XP | 制造商:Littelfuse 功能描述:FUSE - MCASE 32V 20A 1-PC CARD 制造商:Littelfuse 功能描述:RETAIL / FUSE - MCASE 32V 20A 1-pc Card |

| MCAS025.XP | 制造商:Littelfuse 功能描述:FUSE - MCASE 32V 25A 1-PC CARD 制造商:Littelfuse 功能描述:RETAIL / FUSE - MCASE 32V 25A 1-pc Card |

| MCAS030.XP | 制造商:Littelfuse 功能描述:FUSE - MCASE 32V 30A 1-PC CARD |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。