- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45291 > MC9S08RD16CFG (MOTOROLA INC) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | MC9S08RD16CFG |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | LQFP-44 |

| 文件頁(yè)數(shù): | 33/232頁(yè) |

| 文件大小: | 2818K |

| 代理商: | MC9S08RD16CFG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)

Timer/PWM Module (TPM) Module

MC9S08RC/RD/RE/RG

128

MOTOROLA

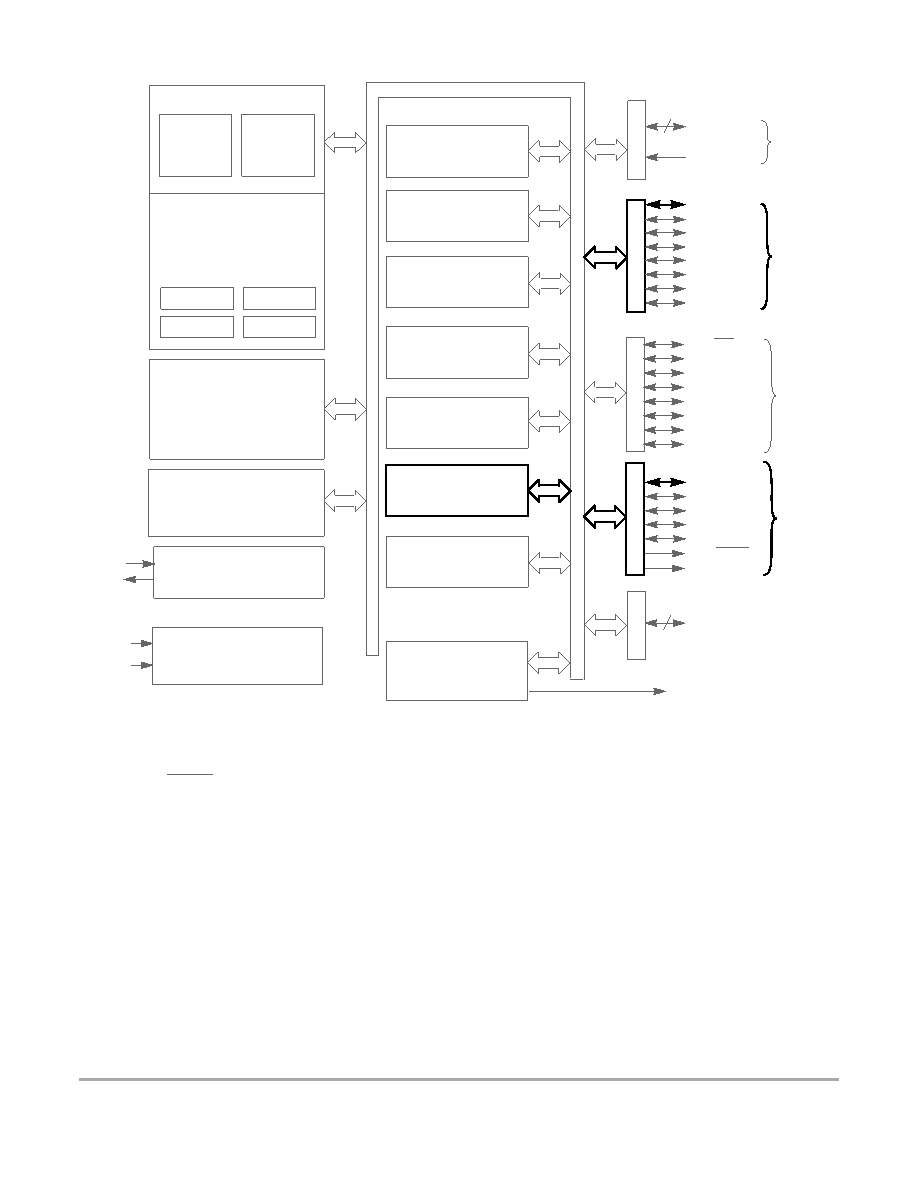

Figure 10-1 MC9S08RC/RD/RE/RG Block Diagram Highlighting TPM Block and Pins

PTD3

PTD4/ACMP1–

PTD5/ACMP1+

PTD6/TPM1CH0

PTC1/KBI2P1

PTC0/KBI2P0

VSS

VDD

PTB3

PTB2

PTA7/KBI1P7–

PTB0/TxD1

PTB1/RxD1

PTD2/IRQ

PTD1/RESET

PTD0/BKGD/MS

PTC7/SS1

PTC6/SPSCK1

PTC5/MISO1

PTC4/MOSI1

PTC3/KBI2P3

PTC2/KBI2P2

POR

T

A

POR

T

C

POR

T

D

POR

T

B

8-BIT KEYBOARD

INTERRUPT MODULE (KBI1)

SERIAL PERIPHERAL

INTERFACE MODULE (SPI1)

USER FLASH

USER RAM

(RC/RD/RE/RG32/60 = 2048 BYTES)

DEBUG

MODULE (DBG)

(RC/RD/RE/RG60 = 63,364 BYTES)

HCS08 CORE

NOTES:

1. Port pins are software configurable with pullup device if input port

2. PTA0 does not have a clamp diode to VDD. PTA0 should not be driven above VDD.

3. IRQ pin contains software configurable pullup/pulldown device if IRQ enabled (IRQPE = 1)

4. The RESET pin contains integrated pullup device enabled if reset enabled (RSTPE = 1)

5. High current drive

6. Pins PTA[7:0] contain both pullup and pulldown devices. Pulldown available when KBI enabled (KBI1Pn = 1).

NOTES

NOTES 1, 5

2-CHANNEL TIMER/PWM

MODULE (TPM1)

PTE7–

POR

T

E

PTB5

PTB4

PTE6

PTB7/TPM1CH1

MODULE (ACMP1)

HCS08 SYSTEM CONTROL

RESETS AND INTERRUPTS

MODES OF OPERATION

POWER MANAGEMENT

VOLTAGE

REGULATOR

RTI

ANALOG COMPARATOR

COP

IRQ

LVD

INTERNAL BUS

LOW-POWER OSCILLATOR

INTERFACE MODULE (SCI1)

SERIAL COMMUNICATIONS

7

PTA1/KBI1P1

8

PTE0

NOTE 1

NOTES1, 2

NOTE 1

(RC/RD/RE/RG32 = 32,768 BYTES)

(RC/RD/RE8/16 = 1024 BYTES)

(RC/RD/RE16 = 16,384 BYTES)

XTAL

EXTAL

CARRIER MODULATOR

TIMER MODULE (CMT)

1, 3, 4

4-BIT KEYBOARD

INTERRUPT MODULE (KBI2)

IRO NOTE 5

PTA0/KBI1P0

(RC/RD/RE8 = 8192 BYTES)

BDC

CPU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9S08RD16CPE | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP28 |

| MC9S08RD60CFG | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| MC9S08RG32CFG | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| MC9S08RC8CFG | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| MC9S08RC8CFJ | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC9S08RD16CFGE | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC9S08RD16CFJ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC9S08RD16CFJE | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC9S08RD16CPE | 功能描述:8位微控制器 -MCU 8 BIT 16K FLASH RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| MC9S08RD16DWE | 功能描述:8位微控制器 -MCU SOIC CYGNUS LEAD FREE RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。