- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371077 > MC92053 (Motorola, Inc.) Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 PDF資料下載

參數(shù)資料

| 型號: | MC92053 |

| 廠商: | Motorola, Inc. |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 中文描述: | Ultraframer DS3/E3/DS2/E2/DS1/E1/DS0 |

| 文件頁數(shù): | 2/6頁 |

| 文件大小: | 45K |

| 代理商: | MC92053 |

Motorola

MC92053

2

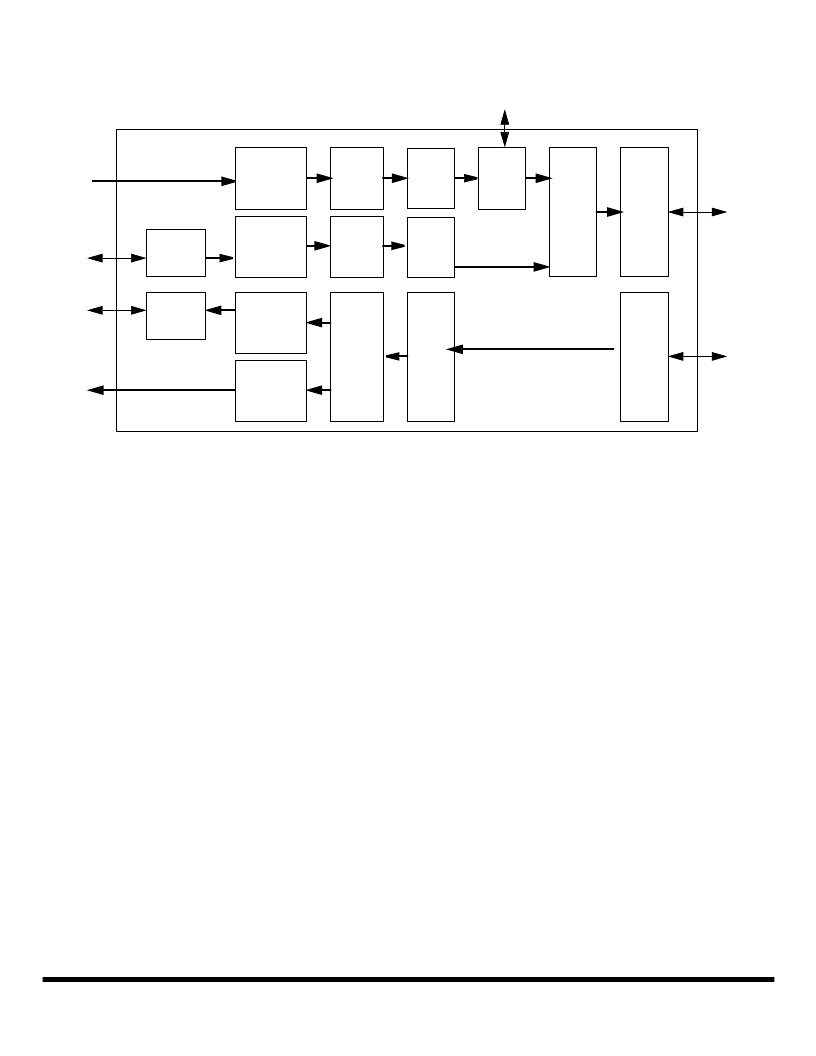

Figure 2. Framer Block Diagram

General Description

The MC92053 implements four copies of the TC sublay-

er of the DAVIC asymmetrical FTTC PHY specification

for network devices. The MC92053 key functional

blocks are described in the paragraphs which follow.

Tx UTOPIA Interface

The Transmit UTOPIA interface accepts ATM cells from

the ATM layer according to the UTOPIA Level 2 speci-

fication. Each cell is stored in one of the four transmit

cell FIFO’s. This block uses TXCLK provided by the

ATM layer. The FIFO’s are used for rate adaptation be-

tween TXCLK (the UTOPIA interface clock) and the de-

vice clock.

Rx UTOPIA Interface

The receive UTOPIA interface reads ATM cells from the

four receive cell FIFO’s and transfers them to the ATM

layer according to the ATM Forum UTOPIA Level 2

specification. This block uses RXCLK provided by the

ATM layer. The FIFO is used for rate adaptation be-

tween RXCLK (the UTOPIA interface clock) and the de-

vice clock.

Microprocessor Interface

The microprocessor interface is an 8-bit generic slave

interface. It is used for initializing the internal registers

and reading status registers and counters.

JTAG

The MC92053 provides JTAG boundary scan.

Framers

Each of the four framers performs the TC functions for

a single user. The blocks contained in a framer are

shown in Figure 2 and are described in the paragraphs

which follow.

Tx Cell Functions

The transmit cell functions block reads ATM cells from

a transmit cell FIFO. If there are no cells available when

a downstream frame should be transmitted, the cell

functions block generates an idle cell. It calculates the

HEC value based on the ATM header of each cell and

inserts it in the fifth octet of the cell. This block also ran-

domizes the payload of the ATM cells according to

ITU-T Recommendation I.432.

A count of the cells transferred from the transmit cell

FIFO is maintained.

Data Link Insertion Block

The data link insertion block provides direct serial ac-

cess to the data link bytes of the downstream frame

headers. The data link stream for the downstream

frames is optionally inserted using an output clock pin

and an input data pin. The device ID to which the data

link stream is destined is programmable.

Framing

Inter-

leaver

Random-

izer

Tx

PMD

I/F

Reed-

Solomon

Decoder

Deran-

domizer

Rx

PMD

I/F

Reed-

Solomon

Encoder

Tx Cell

Functions

Data

Link

Insertion

Reed-

Solomon

Encoder

Random-

izer

Frame

Header

Interpretation

Rx Cell

Functions

Data

Link

Extraction

Frame

Header

Generation

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC92300 | VITERBI Decoder for Digital TV |

| MC92300CG | VITERBI Decoder for Digital TV |

| MC92305 | 16/32/64/128/256 QAM RECEIVER AND REED-SOLOMON DECODER |

| MC92305CD | 16/32/64/128/256 QAM RECEIVER AND REED-SOLOMON DECODER |

| MC92315 | DVB-T(Digital Video Broadcast - Terrestrial) Demodulator(DVB-T數(shù)字視頻通信解調(diào)器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC92101CO | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC921G | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC92300 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:VITERBI Decoder for Digital TV |

| MC92300CG | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:VITERBI Decoder for Digital TV |

| MC92303 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:QPSK/BPSK DIGITAL DEMODULATOR |

發(fā)布緊急采購,3分鐘左右您將得到回復。