- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25639 > MC80C52XXX-16SHXXX (ATMEL CORP) 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | MC80C52XXX-16SHXXX |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CDIP40 |

| 封裝: | 0.600 INCH, SIDE BRAZED, DIP-40 |

| 文件頁數(shù): | 7/80頁 |

| 文件大小: | 5152K |

| 代理商: | MC80C52XXX-16SHXXX |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

199

2466T–AVR–07/10

ATmega16(L)

Combining Several

TWI Modes

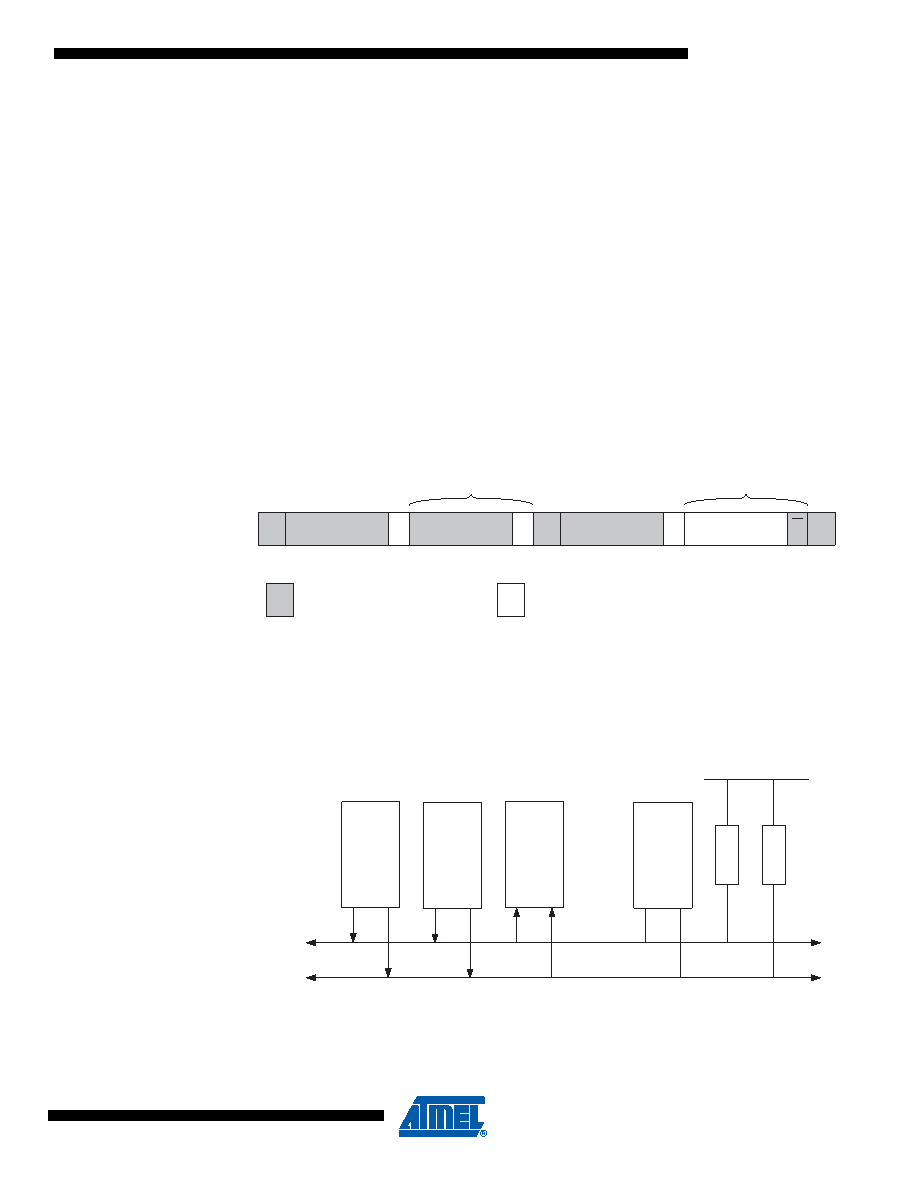

In some cases, several TWI modes must be combined in order to complete the desired action.

Consider for example reading data from a serial EEPROM. Typically, such a transfer involves

the following steps:

1.

The transfer must be initiated

2.

The EEPROM must be instructed what location should be read

3.

The reading must be performed

4.

The transfer must be finished

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct

the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data

must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must

be changed. The Master must keep control of the bus during all these steps, and the steps

should be carried out as an atomical operation. If this principle is violated in a multi-master sys-

tem, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the

Master will read the wrong data location. Such a change in transfer direction is accomplished by

transmitting a REPEATED START between the transmission of the address byte and reception

of the data. After a REPEATED START, the Master keeps ownership of the bus. The following

figure shows the flow in this transfer.

Figure 94. Combining Several TWI Modes to Access a Serial EEPROM

Multi-master

Systems and

Arbitration

If multiple Masters are connected to the same bus, transmissions may be initiated simultane-

ously by one or more of them. The TWI standard ensures that such situations are handled in

such a way that one of the Masters will be allowed to proceed with the transfer, and that no data

will be lost in the process. An example of an arbitration situation is depicted below, where two

Masters are trying to transmit data to a Slave Receiver.

Figure 95. An Arbitration Example

Master Transmitter

Master Receiver

S = START

Rs = REPEATED START

P = STOP

Transmitted from Master to Slave

Transmitted from Slave to Master

S

SLA+W

A

ADDRESS

A

Rs

SLA+R

A

DATA

A

P

Device 1

MASTER

TRANSMITTER

Device 2

MASTER

TRANSMITTER

Device 3

SLAVE

RECEIVER

Device n

SDA

SCL

........

R1

R2

V

CC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MD80C52EXXX-20 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| MC80C52CXXX-12SB | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CDIP40 |

| MQ80C32-25SCD | 8-BIT, 25 MHz, MICROCONTROLLER, CQFP44 |

| MQ80C32E-20SHXXX:D | 8-BIT, 20 MHz, MICROCONTROLLER, CQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC80D21000G | 制造商:COR 功能描述:RN |

| MC80F0104 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0204 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。