- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄25623 > MC80C32-36SC (ATMEL CORP) 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | MC80C32-36SC |

| 廠(chǎng)商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 36 MHz, MICROCONTROLLER, CDIP40 |

| 封裝: | 0.600 INCH, SIDE BRAZED, DIP-40 |

| 文件頁(yè)數(shù): | 46/132頁(yè) |

| 文件大小: | 10886K |

| 代理商: | MC80C32-36SC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)當(dāng)前第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)

212

ATmega8535(L)

2502K–AVR–10/06

Note:

1. Depending on the state of CKADC2.

Differential Gain Channels

When using differential gain channels, certain aspects of the conversion need to be

taken into consideration.

Differential conversions are synchronized to the internal clock CK

ADC2 equal to half the

ADC clock. This synchronization is done automatically by the ADC interface in such a

way that the sample-and-hold occurs at a specific phase of CK

ADC2. A conversion initi-

ated by the user (i.e., all single conversions, and the first free running conversion) when

CK

ADC2 is low will take the same amount of time as a single ended conversion (13 ADC

clock cycles from the next prescaled clock cycle). A conversion initiated by the user

when CK

ADC2 is high will take 14 ADC clock cycles due to the synchronization mecha-

nism. In free running mode, a new conversion is initiated immediately after the previous

conversion completes, and since CK

ADC2 is high at this time, all automatically started

(i.e., all but the first) free running conversions will take 14 ADC clock cycles.

The gain stage is optimized for a bandwidth of 4 kHz at all gain settings. Higher frequen-

cies may be subjected to non-linear amplification. An external low-pass filter should be

used if the input signal contains higher frequency components than the gain stage band-

width. Note that the ADC clock frequency is independent of the gain stage bandwidth

limitation. For example, the ADC clock period may be 6 s, allowing a channel to be

sampled at 12 kSPS, regardless of the bandwidth of this channel.

If differential gain channels are used and conversions are started by Auto Triggering, the

ADC must be switched off between conversions. When Auto Triggering is used, the

ADC prescaler is reset before the conversion is started. Since the gain stage is depen-

dent of a stable ADC clock prior to the conversion, this conversion will not be valid. By

disabling and then re-enabling the ADC between each conversion (writing ADEN in

ADCSRA to “0” then to “1”), only extended conversions are performed. The result from

the extended conversions will be valid. See “Prescaling and Conversion Timing” on

page 209 for timing details.

Changing Channel or

Reference Selection

The MUXn and REFS1:0 bits in the ADMUX Register are single buffered through a tem-

porary register to which the CPU has random access. This ensures that the channels

and reference selection only takes place at a safe point during the conversion. The

channel and reference selection is continuously updated until a conversion is started.

Once the conversion starts, the channel and reference selection is locked to ensure a

sufficient sampling time for the ADC. Continuous updating resumes in the last ADC

clock cycle before the conversion completes (ADIF in ADCSRA is set). Note that the

conversion starts on the following rising ADC clock edge after ADSC is written. The user

is thus advised not to write new channel or reference selection values to ADMUX until

one ADC clock cycle after ADSC is written.

If Auto Triggering is used, the exact time of the triggering event can be indeterminable.

Special care must be taken when updating the ADMUX Register, in order to control

which conversion will be affected by the new settings.

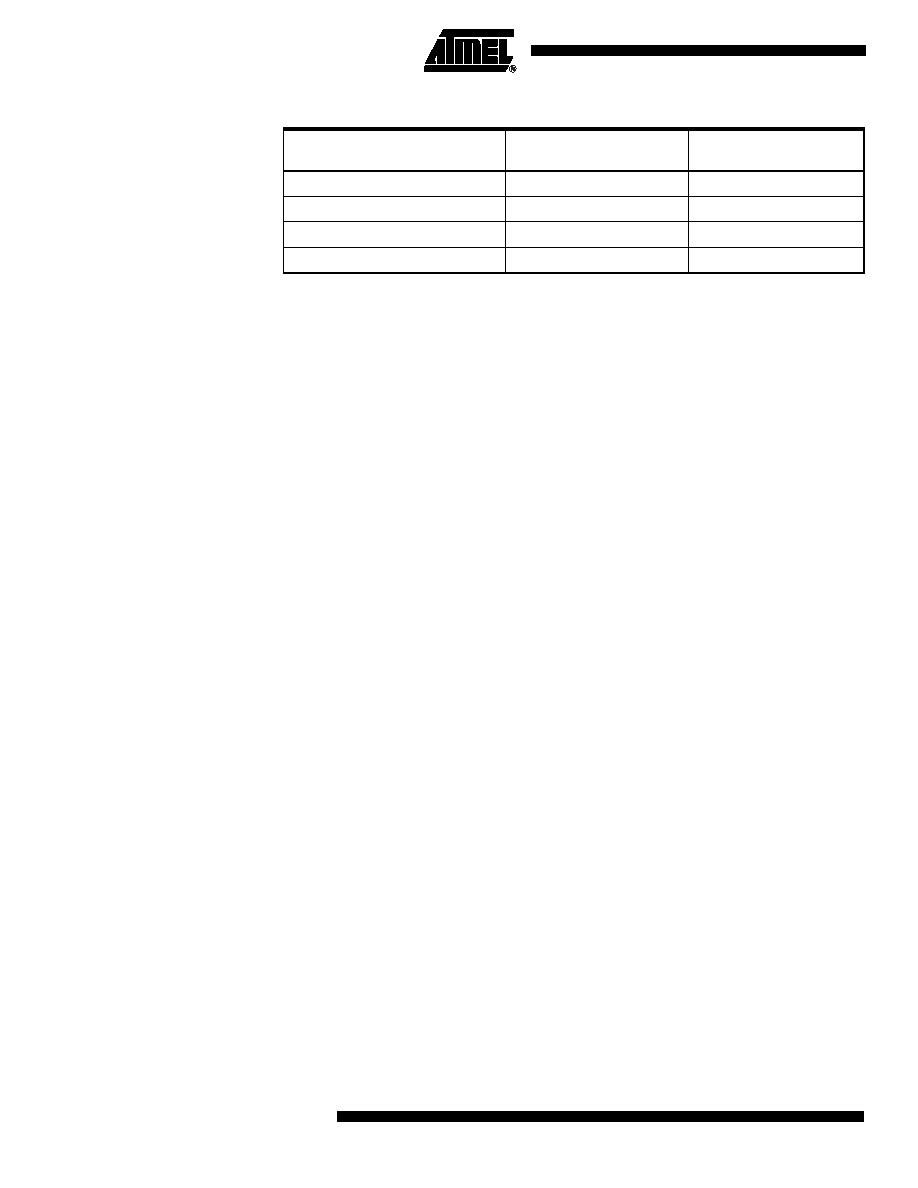

Table 82. ADC Conversion Time

Condition

Sample & Hold (Cycles

from Start of Conversion)

Conversion Time

(Cycles)

First conversion

14.5

25

Normal conversions, single ended

1.5

13

Auto Triggered conversions

2

13.5

Normal conversions, differential

1.5/2.5(1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MR80C52XXX-36P883R | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| MQ80C52XXX-36SHXXX | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQFP44 |

| MC80C32E-16SHXXX:D | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52XXX-36SCD | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, CQCC44 |

| MD80C32-16SHXXX | 8-BIT, 16 MHz, MICROCONTROLLER, CDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC-80C32E-30 | 制造商:AIMTEC 制造商全稱(chēng):AIMTEC 功能描述:Rad. Tolerant 8-bit ROMless Microcontroller |

| MC-80C32E-30-E | 制造商:AIMTEC 制造商全稱(chēng):AIMTEC 功能描述:Rad. Tolerant 8-bit ROMless Microcontroller |

| MC80D21000G | 制造商:COR 功能描述:RN |

| MC80F0104 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| MC80F0104B | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。