- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369902 > MC68HC000CFN10 (Motorola, Inc.) Addendum to M68000 User Manual PDF資料下載

參數(shù)資料

| 型號: | MC68HC000CFN10 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Addendum to M68000 User Manual |

| 中文描述: | 增編M68000用戶手冊 |

| 文件頁數(shù): | 5/26頁 |

| 文件大?。?/td> | 124K |

| 代理商: | MC68HC000CFN10 |

5

M68000 USER’S MANUAL ADDENDUM

MOTOROLA

power consumption to its quiescent value

low-power mode described below will be routinely tested as part of the MC68SEC000 test vectors provided

by Motorola.

1

while maintaining the internal state of the processor. The

To successfully enter the low-power mode, the MC68SEC000 must first be in the supervisor mode. A

recommended method for entering the low-power mode is to use the TRAP instruction, which causes the

processor to begin exception processing, thus entering the supervisor mode. External circuitry should

accomplish the following steps during the trap routine:

1.

Externally detect a write to the low-power address. You select this address which can be any address

in the 16 Mbyte addressing range of the MC68SEC000. A write to the low-power address can be

detected by polling A23–A0, R/W, and FC2–FC0. When the low-power address is detected, R/W is

a logic low, and the function codes have a five (101) on their output, the processor is writing to the

low-power address in supervisor mode and user-designed circuitry should assert the

ADDRESS_MATCH signal shown in Figure 2 and Figure 3.

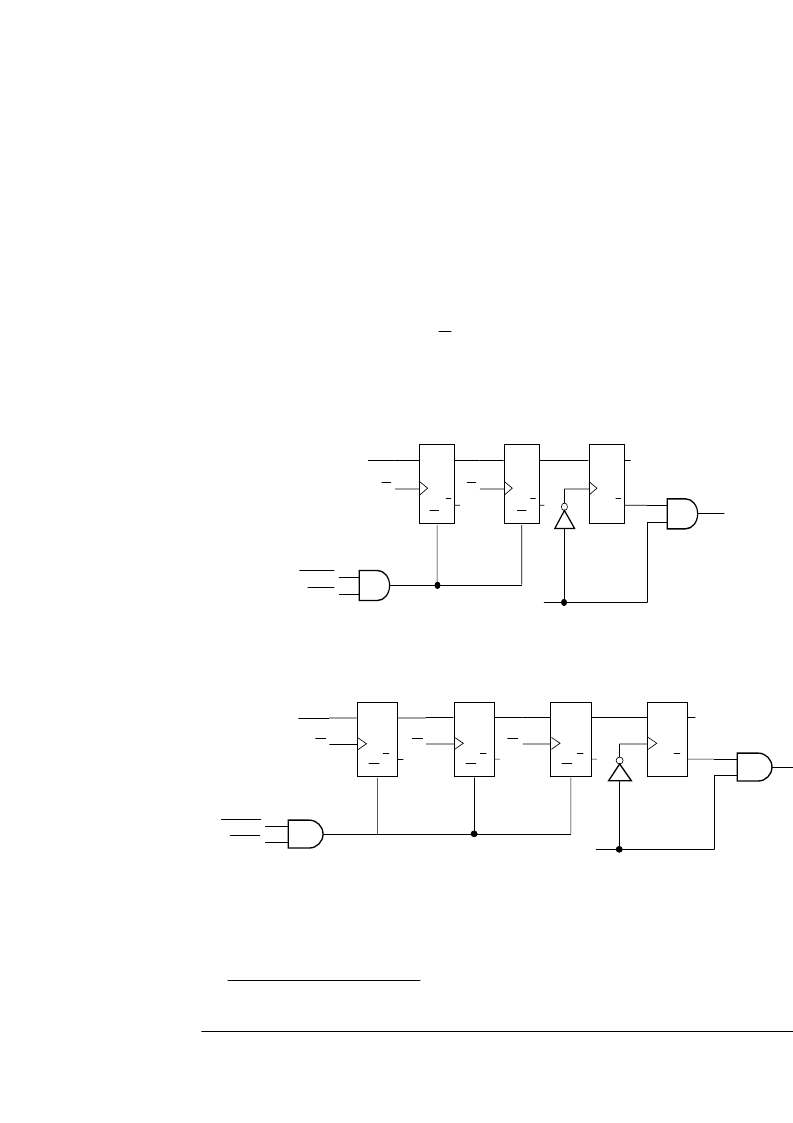

Figure 3. MC68SEC000 Low-Power Circuitry for 8-Bit Data Bus

2.

Execute the STOP instruction. The external circuitry shown in Figure 2 and Figure 3 will count the

number of bus cycles starting with the write to the low-power address and will stop the processor

clock on the first falling edge of the system clock after the bus cycle that reads the immediate data

of the STOP instruction. Figure 3 has one more flip-flop than Figure 2 because the MC68SEC000 in

1.

The preliminary specification for the MC68SEC000’s current drain while in the low-power mode is Idd < 2

Idd < 5

μ

A for 5.0V operation.

μ

A for 3.3V operation and

Figure 2. MC68SEC000 Low-Power Circuitry for 16-Bit Data Bus

D

Q

Q

CL

CK

D

Q

CK

D

Q

CK

ADDRESS_MATCH

AS

RESTART

RESET

CPU_CLK

SYSTEM_CLK

Q

Q

AS

CL

D

Q

Q

CL

CK

D

Q

Q

CL

CK

D

Q

Q

CK

ADDRESS_MATCH

RESTART

RESET

CPU_CL

D

Q

Q

CL

CK

SYSTEM_CLK

AS

AS

AS

相關PDF資料 |

PDF描述 |

|---|---|

| MC68HC000CFN12 | Addendum to M68000 User Manual |

| MC68HC000CFN16 | Addendum to M68000 User Manual |

| MC68HC000CFN20 | Addendum to M68000 User Manual |

| MC68HC000CFN8 | Addendum to M68000 User Manual |

| MC68HC000FN10 | Addendum to M68000 User Manual |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC000CFN10R2 | 制造商:Rochester Electronics LLC 功能描述:16-BIT MPU - Bulk |

| MC68HC000CFN12 | 制造商:Rochester Electronics LLC 功能描述:16-BIT MPU - Bulk |

| MC68HC000CFN12R2 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HC000CFN16 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Addendum to M68000 User Manual |

| MC68HC000CFN20 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Addendum to M68000 User Manual |

發(fā)布緊急采購,3分鐘左右您將得到回復。