- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25625 > MC3S12XEP100F1CAL (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP112 PDF資料下載

參數(shù)資料

| 型號(hào): | MC3S12XEP100F1CAL |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP112 |

| 封裝: | LQFP-112 |

| 文件頁數(shù): | 68/1324頁 |

| 文件大?。?/td> | 8453K |

| 代理商: | MC3S12XEP100F1CAL |

Chapter 27 512 KByte Flash Module (S12XFTM512K3V1)

MC9S12XE-Family Reference Manual , Rev. 1.21

Freescale Semiconductor

1059

Upon clearing CCIF to launch the Verify Backdoor Access Key command, the Memory Controller will

check the FSEC KEYEN bits to verify that this command is enabled. If not enabled, the Memory

Controller sets the ACCERR bit in the FSTAT register and terminates. If the command is enabled, the

Memory Controller compares the key provided in FCCOB to the backdoor comparison key in the Flash

conguration eld with Key 0 compared to 0x7F_FF00, etc. If the backdoor keys match, security will be

released. If the backdoor keys do not match, security is not released and all future attempts to execute the

Verify Backdoor Access Key command are aborted (set ACCERR) until a reset occurs. The CCIF flag is

set after the Verify Backdoor Access Key operation has completed.

27.4.2.13 Set User Margin Level Command

The Set User Margin Level command causes the Memory Controller to set the margin level for future read

operations of a specific P-Flash or D-Flash block.

Upon clearing CCIF to launch the Set User Margin Level command, the Memory Controller will set the

user margin level for the targeted block and then set the CCIF ag.

Valid margin level settings for the Set User Margin Level command are dened in Table 27-58.

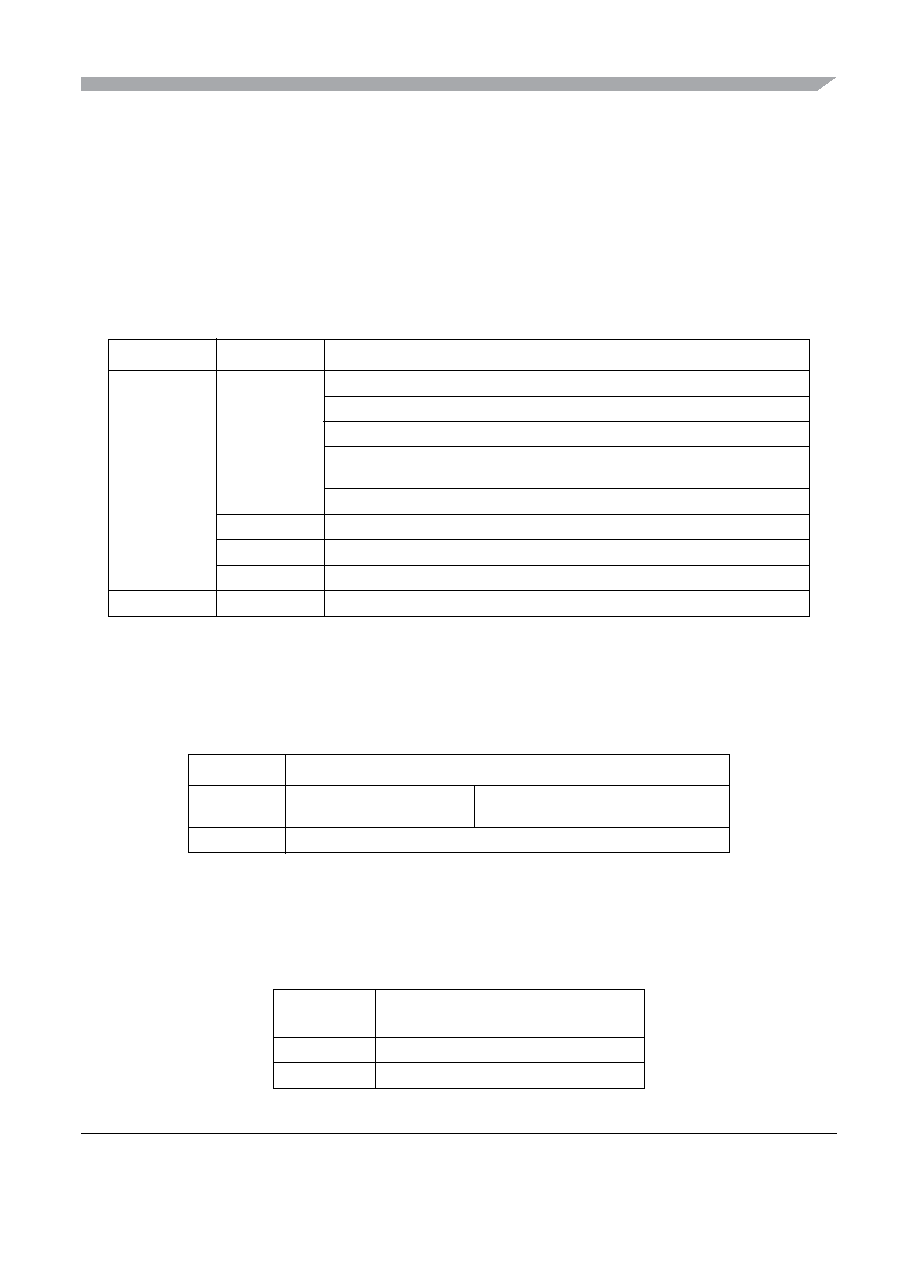

Table 27-56. Verify Backdoor Access Key Command Error Handling

Register

Error Bit

Error Condition

FSTAT

ACCERR

Set if CCOBIX[2:0] != 100 at command launch

Set if a Load Data Field command sequence is currently active

Set if an incorrect backdoor key is supplied

Set if backdoor key access has not been enabled (KEYEN[1:0] != 10, see

Set if the backdoor key has mismatched since the last reset

FPVIOL

None

MGSTAT1

None

MGSTAT0

None

FERSTAT

EPVIOLIF

None

Table 27-57. Set User Margin Level Command FCCOB Requirements

CCOBIX[2:0]

FCCOB Parameters

000

0x0D

Global address [22:16] to identify the

Flash block

001

Margin level setting

Table 27-58. Valid Set User Margin Level Settings

CCOB

(CCOBIX=001)

Level Description

0x0000

Return to Normal Level

0x0001

User Margin-1 Level(1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC9S12XEP100F1CALR | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP112 |

| MC9S12XEP100F1VAAR | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP80 |

| MC9S12XEP100J1CAA | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP80 |

| MC3S12XEP100F1MAGR | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, QFP144 |

| MC9S12XEP100F1MAAR | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, QFP80 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC3S12XEP100F1CALR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCS12X Microcontrollers |

| MC3S12XEP100F1CVLR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCS12X Microcontrollers |

| MC3S12XEP100F1MAAR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCS12X Microcontrollers |

| MC3S12XEP100F1MAGR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCS12X Microcontrollers |

| MC3S12XEP100F1MALR | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:HCS12X Microcontrollers |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。