- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369899 > MC145444P (Motorola, Inc.) Single-Chip 300-Baud Modem PDF資料下載

參數(shù)資料

| 型號(hào): | MC145444P |

| 廠商: | Motorola, Inc. |

| 英文描述: | Single-Chip 300-Baud Modem |

| 中文描述: | 單芯片300波特調(diào)制解調(diào)器 |

| 文件頁數(shù): | 5/12頁 |

| 文件大?。?/td> | 161K |

| 代理商: | MC145444P |

MC145444

MOTOROLA

5

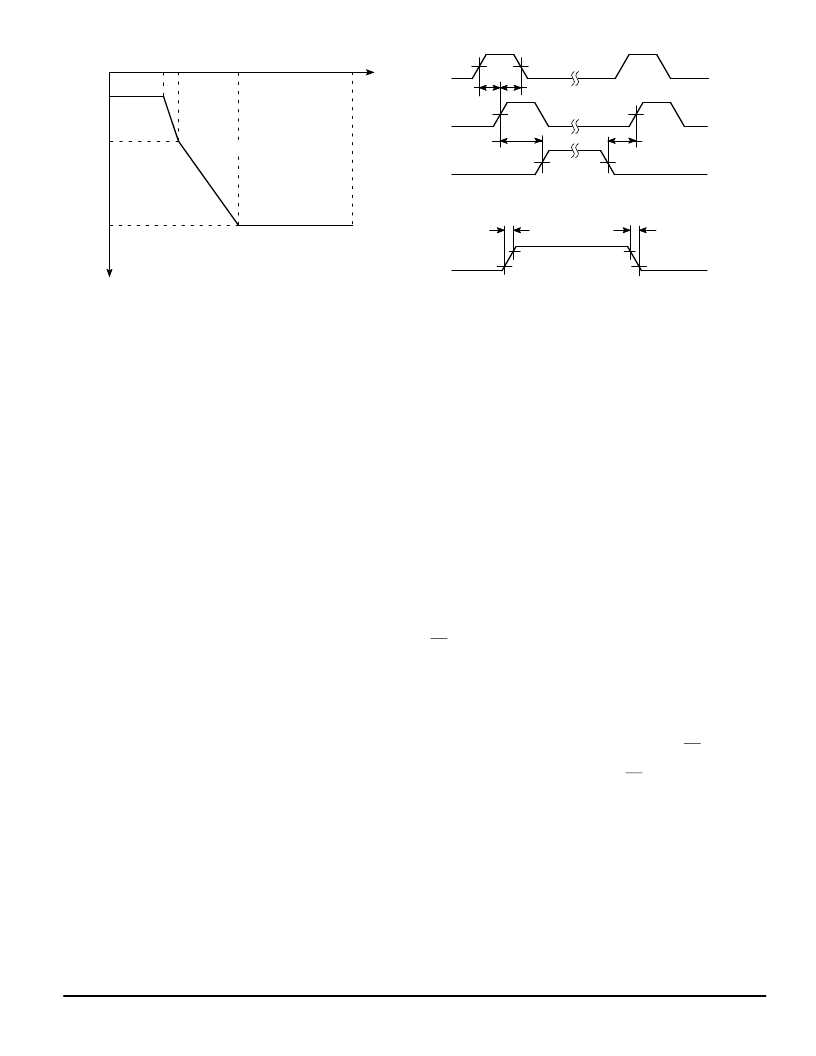

Figure 1. Out–of–Band Energy

Figure 2. Switching Characteristics

– 55

– 15 dB/OCT.

f (Hz)

256 k

16 k

4 k

3.4 k

0

0

– 25

50%

50%

DATA

SCK

ENB

ENB

50%

50%

50%

PREVIOUS

DATA LATCHED

LAST

CLK

FIRST

CLK

tsu

th

tr

tf

tsu

trec

— VCC

— GND

— VCC

— GND

— VCC

— GND

— VCC

— GND

PIN DESCRIPTION

VCC

Positive Power Supply (Pin 15)

This pin is normally tied to the + 5.0 V. A 0.1

μ

F decoupling

capacitor should be used.

GND

Ground Pin (Pin 5)

This pin is normally tied to 0 V.

GNDA

Analog Ground (Pin 3)

Analog ground is internally biased to (VCC – VSS)/2. It

should be tied to ground through a 0.1

μ

F and 100

μ

F

capacitor.

X1

Crystal Oscillator Output (Pin 7)

Connecting a 3.579545 MHz

±

0.1% crystal between X1

and X2 will cause the transmit frequencies to be within

±

64 MHz of nominal. X1 is capable of driving several CMOS

gates. An external clock may be applied to X2. X1 should

then be left open.

X2

Crystal Oscillator Input (Pin 8)

Refer to X1.

SCK

Shift Resister Clock Input (Pin 13)

This pin is the clock input for the 15–bit shift register. Serial

data is loaded into the shift register on the rising edge of this

clock.

DATA

Serial Data Input (Pin 12)

This pin is the 15–bit serial data input. This data deter-

mines the mode, DTMF signal, transmit attenuation, carrier

detect time, channel, and transmit squelch.

ENB

Enable Input (Pin 14)

Data is loaded into the 15–bit shift register when this pin is

at a logic low. When this pin transitions from a logic high to

low, the data is transferred to the internal latch on the falling

edge of ENB. New data loaded into the shift register will not

affect the device operation until this pin transitions from high

to low. (See Figure 2.)

TxD

Transmit Data Input (Pin 11)

This pin is the transmit data input, The mark frequency is

generated when this pin is at the logic high level. The space

frequency is generated when the pin is at a logic low.

RxD

Receive Data Output (Pin 10)

This pin is the receive data output. A high logic level of this

pin indicates that the mark carrier frequency has been re-

ceived, and a low logic level indicates the space carrier fre-

quency has been received.

SD

Carrier/Call Progress Tone Detect (Pin 9)

This pin is the output from the carrier detector or call prog-

ress tone detector. This pin works as a carrier detector in the

FSK mode and as the call progress tone detector in the

CPTD mode. The output goes to a logic low level when the

input signal reaches the minimum threshold of the detect

level that is adjusted by the CDA voltage. When SD = H, the

receive data output (RxD) is clamped high to avoid errors

that may occur with loop noise. The SD pin is also clamped

high in the other modes except during the power–down

mode.

TxA1

Non–Inverting Transmit Analog Carrier Output (Pin 18)

This pin is the line driver non–inverting output of the FSK

and tone transmit analog signals. A + 6 dBm (max) differen-

tial output voltage can be obtained by connecting a 1.2 k

load resistor between Tx1 and Tx2. Attention must be set so

as not to exceed this level when an external input is added

to the DSI pin. A telephone line (600

) is driven through an

external 600

resistor. In this case, the output level be-

comes about half of differential output.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC145446AFW | Single-Chip 300-Baud Modem with DTMF Transceiver |

| MC145446A | Single-Chip 300-Baud Modem with DTMF Transceiver |

| MC145446 | Single-Chip 300-Baud Modem with DTMF Transceiver |

| MC145447DW | Calling Line Identification(CLID) Receiver with Ring Detector |

| MC145447 | Calling Line Identification(CLID) Receiver with Ring Detector |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC145446AFW | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Motorola Inc 功能描述: 制造商:MOTOROLA 功能描述: |

| MC145447DW | 制造商:Motorola Inc 功能描述:CALLER NUMBER ID CIRCUIT, 16 Pin, Plastic, SOP |

| MC145447DWR2 | 制造商:Motorola Inc 功能描述:TELEPHONE MULTIFUNCTION CKT, 16 Pin Plastic SOP |

| MC145447P | 制造商:Motorola Inc 功能描述: |

| MC145475DW | 制造商:Motorola Inc 功能描述:DATACOM, ISDN CONTROLLER, PDSO28 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。