- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371014 > MC14517BDWR2 (ON SEMICONDUCTOR) Dual 64-Bit Static Shift Register PDF資料下載

參數(shù)資料

| 型號: | MC14517BDWR2 |

| 廠商: | ON SEMICONDUCTOR |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual 64-Bit Static Shift Register |

| 中文描述: | 4000/14000/40000 SERIES, 64-BIT RIGHT SERIAL IN SERIAL OUT SHIFT REGISTER, TRUE OUTPUT, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 3/6頁 |

| 文件大?。?/td> | 209K |

| 代理商: | MC14517BDWR2 |

MOTOROLA CMOS LOGIC DATA

405

MC14517B

Output Rise and Fall Time

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

tTLH, tTHL = (0.65 ns/pF) CL + 9.5 ns

Propagation Delay Time

tPLH, tPHL = (1.7 ns/pF) CL + 390 ns

tPLH, tPHL = (0.66 ns/pF) CL + 177 ns

tPLH, tPHL = (0.5 ns/pF) CL + 115 ns

Clock Pulse Width

tTLH, tTHL

5.0

10

15

—

—

—

100

50

40

200

100

80

ns

tPLH, tPHL

5.0

10

15

—

—

—

475

210

140

770

300

215

ns

tWH

5.0

10

15

330

125

100

170

75

60

—

—

—

ns

Clock Pulse Frequency

fcl

5.0

10

15

—

—

—

3.0

6.7

8.3

1.5

4.0

5.3

MHz

Clock Pulse Rise and Fall Time

tTLH, tTHL

5.0

10

15

**See Note

—

Data to Clock Setup Time

tsu

5.0

10

15

0

10

15

– 40

– 15

0

—

—

—

ns

Data to Clock Hold Time

th

5.0

10

15

150

75

35

75

25

10

—

—

—

ns

Write Enable to Clock Setup Time

tsu

5.0

10

15

400

200

110

170

65

50

—

—

—

ns

Write Enable to Clock Release Time

trel

5.0

10

15

380

180

100

160

55

40

—

—

—

ns

*The formulas given are for the typical characteristics only at 25 C.

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

** When shift register sections are cascaded, the maximum rise and fall time of the clock input should be equal to or less than the rise and fall

time of the data outputs, driving data inputs, plus the propagation delay of the output driving stage.

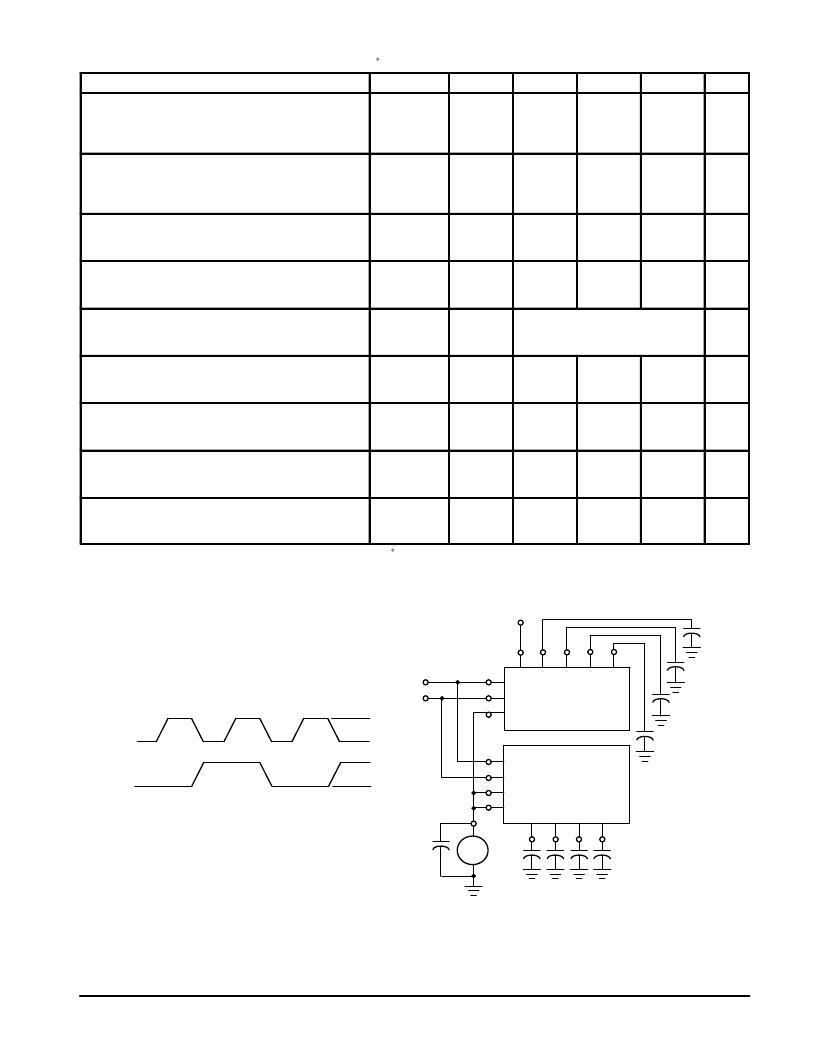

Figure 1. Power Dissipation Test Circuit and Waveform

CL

CL

CL

CL

CL

CL

CL

CL

VDD

Q16 Q32 Q48 Q64

Q16 Q32 Q48 Q64

VDD

VDD

VSS

VSS

D

C

WE

D

C

WE

VSS

ID

D

C

50

μ

F

REPETITIVE WAVEFORM

C

D

fo

(f = 1/2 fo)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC14517BCP | Non-inverting High Speed MOSFET Driver with Active Pullup and Internal Regulator 5-SOT-23 |

| MC14517BDW | Dual 64-Bit Static Shift Register |

| MC145170D1 | LOW-VOLTAGE CMOS OCTAL BUFFER |

| MC14517 | LOW-VOLTAGE CMOS OCTAL BUFFER |

| MC14517BCP | Dual 64-Bit Static Shift Register |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC14517BDWR2G | 功能描述:計數(shù)器移位寄存器 3-18V Dual 64-Bit Static Shift RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BCP | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BCPG | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BDW | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

| MC14518BDWG | 功能描述:計數(shù)器移位寄存器 3-18V Dual BCD Up RoHS:否 制造商:Texas Instruments 計數(shù)器類型: 計數(shù)順序:Serial to Serial/Parallel 電路數(shù)量:1 封裝 / 箱體:SOIC-20 Wide 邏輯系列: 邏輯類型: 輸入線路數(shù)量:1 輸出類型:Open Drain 傳播延遲時間:650 ns 最大工作溫度:+ 125 C 最小工作溫度:- 40 C 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。