- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379302 > MC10H640FN (MOTOROLA INC) 68030/040 PECL-TTL CLOCK DRIVER PDF資料下載

參數(shù)資料

| 型號(hào): | MC10H640FN |

| 廠商: | MOTOROLA INC |

| 元件分類: | 時(shí)鐘及定時(shí) |

| 英文描述: | 68030/040 PECL-TTL CLOCK DRIVER |

| 中文描述: | 10H SERIES, LOW SKEW CLOCK DRIVER, 6 TRUE OUTPUT(S), 2 INVERTED OUTPUT(S), PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁(yè)數(shù): | 1/8頁(yè) |

| 文件大小: | 109K |

| 代理商: | MC10H640FN |

SEMICONDUCTOR TECHNICAL DATA

2–1

REV 3

Motorola, Inc. 1996

11/93

The MC10H/100H640 generates the necessary clocks for the 68030,

68040 and similar microprocessors. It is guaranteed to meet the clock

specifications required by the 68030 and 68040 in terms of part–to–part

skew, within–part skew and also duty cycle skew.

The user has a choice of using either TTL or PECL (ECL referenced to

+5.0V) for the input clock. TTL clocks are typically used in present MPU

systems. However, as clock speeds increase to 50MHz and beyond, the

inherent superiority of ECL (particularly differential ECL) as a means of

clock signal distribution becomes increasingly evident. The H640 also

uses differential PECL internally to achieve its superior skew

characteristic.

The H640 includes divide–by–two and divide–by–four stages, both to

achieve the necessary duty cycle skew and to generate MPU clocks as

required. A typical 50MHz processor application would use an input clock

running at 100MHz, thus obtaining output clocks at 50MHz and 25MHz

(see Logic Symbol).

The 10H version is compatible with MECL 10H

ECL logic levels,

while the 100H version is compatible with 100K levels (referenced

to +5.0V).

Generates Clocks for 68030/040

Meets 030/040 Skew Requirements

TTL or PECL Input Clock

Extra TTL and PECL Power/Ground Pins

Asynchronous Reset

Single +5.0V Supply

Function

Reset (R):LOW on RESET forces all Q outputs LOW and all Q outputs HIGH.

Power–Up: The device is designed to have the POS edges of the

÷

2 and

÷

4 outputs synchronized at power up.

Select (SEL):LOW selects the ECL input source (DE/DE). HIGH selects the TTL input source (DT).

The H640 also contains circuitry to force a stable state of the ECL input differential pair, should both sides be left open. In this

case, the DE side of the input is pulled LOW, and DE goes HIGH.

1

VT

VT

Q1

GT

GT

Q0

VT

GT

GT

Q4

Q5

VT

SEL

5

6

7

8

9

10

11

25

24

23

22

21

20

19

Q1

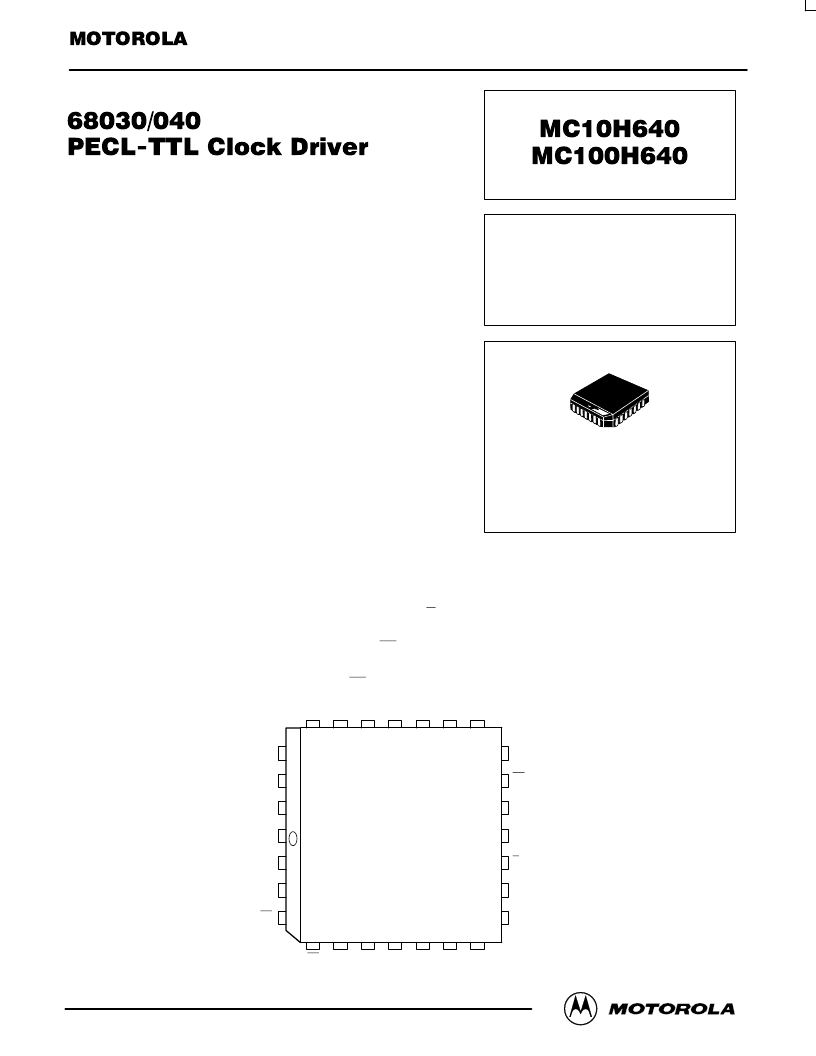

Pinout: 28–Lead PLCC

(Top View)

VBB

DE

DE

VE

R

GE

DT

Q0

VT

VT

Q3

GT

GT

Q2

4

3

2

28

27

26

18

17

16

15

14

13

12

68030/040

PECL–TTL CLOCK

DRIVER

FN SUFFIX

PLASTIC PACKAGE

CASE 776–02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC10H643FN | DUAL SUPPLY ECL-TTL 1:8 CLOCK DRIVER |

| MC10H643 | DUAL SUPPLY ECL-TTL 1:8 CLOCK DRIVER |

| MC10H660FN | 4-Bit ECL/TTL Load Reducing DRAM Driver |

| MC100H660FN | 4-Bit ECL/TTL Load Reducing DRAM Driver |

| MC12028AD | MECL PLL COMPONENTS ±64/65, ±128/129 DUAL MODULUS PRESCALER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC10H640FNG | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 BBG ECL/TTL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| MC10H640FNR2 | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 PECL to TTL Clock RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| MC10H640FNR2G | 功能描述:時(shí)鐘驅(qū)動(dòng)器及分配 PECL to TTL Clock Driver RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| MC10H641FN | 功能描述:轉(zhuǎn)換 - 電壓電平 5V PECL to TTL 1:9 RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時(shí)間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

| MC10H641FNG | 功能描述:轉(zhuǎn)換 - 電壓電平 5V PECL to TTL 1:9 Clock Driver RoHS:否 制造商:Micrel 類型:CML/LVDS/LVPECL to LVCMOS/LVTTL 傳播延遲時(shí)間:1.9 ns 電源電流:14 mA 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MLF-8 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。