- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371002 > MC10125P (MOTOROLA INC) Replaced by SN54LS164 : 8-Bit Parallel-Out Serial Shift Registers 14-CFP -55 to 125 PDF資料下載

參數(shù)資料

| 型號: | MC10125P |

| 廠商: | MOTOROLA INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | Replaced by SN54LS164 : 8-Bit Parallel-Out Serial Shift Registers 14-CFP -55 to 125 |

| 中文描述: | QUAD ECL TO TTL TRANSLATOR, TRUE OUTPUT, PDIP16 |

| 封裝: | PLASTIC, DIP-16 |

| 文件頁數(shù): | 1/7頁 |

| 文件大?。?/td> | 127K |

| 代理商: | MC10125P |

SEMICONDUCTOR TECHNICAL DATA

3–89

REV 5

Motorola, Inc. 1996

3/93

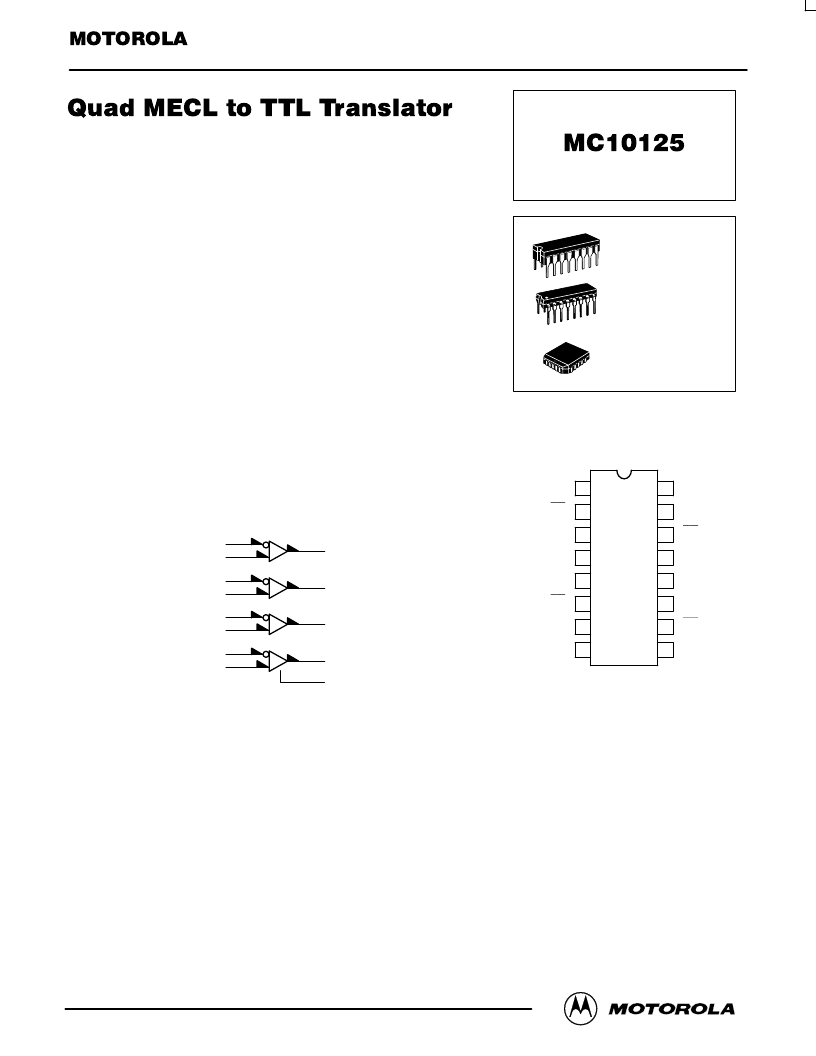

The MC10125 is a quad translator for interfacing data and control signals

between the MECL section and saturated logic sections of digital systems. The

MC10125 incorporates differential inputs and Schottky TTL “totem pole”

outputs. Differential inputs allow for use as an inverting/ non–inverting translator

or as a differential line receiver. The VBB reference voltage is available on pin 1

for use in single–ended input biasing. The outputs of the MC10125 go to a low

logic level whenever the inputs are left floating.

Power supply requirements are ground, +5.0 Volts and –5.2 Volts.

Propagation delay of the MC10125 is typically 4.5 ns. The MC10125 has fanout

of 10 TTL loads. The dc levels are MECL 10,000 in and Schottky TTL, or TTL

out. This device has an input common mode noise rejection of

±

1.0 Volt.

An advantage of this device is that MECL level information can be received,

via balanced twisted pair lines, in the TTL equipment. This isolates the MECL

logic from the noisy TTL environment. This device is useful in computers,

instrumentation, peripheral controllers, test equipment and digital

communications systems.

PD= 380 mW typ/pkg (No Load)

tpd= 4.5 ns typ (50% to + 1.5 Vdc out)

tr, tf= 2.5 ns typ (1.0 V to 2.0 V)

LOGIC DIAGRAM

4

3

2

5

7

6

12

11

10

13

15

14

1

VBB*

*VBB to be used to supply bias to the MC10125 only and bypassed (when used)

with 0.01

μ

F to 0.1

μ

F capacitor to ground (0 V). VBB can source < 1.0 mA.

When the input pin with the bubble goes positive, the output goes negative.

Gnd

VCC (+5.0Vdc) =

VEE (–5.2Vdc) =

=

PIN 16

PIN 9

PIN 8

DIP

PIN ASSIGNMENT

VBB

AIN

AIN

AOUT

BOUT

BIN

BIN

VEE

GND

DIN

DIN

DOUT

COUT

CIN

CIN

VCC

16

15

14

13

12

11

10

9

1

2

3

4

5

6

7

8

Pin assignment is for Dual–in–Line Package.

For PLCC pin assignment, see the Pin Conversion

Tables on page 6–11 of the Motorola MECL Data

Book (DL122/D).

L SUFFIX

CERAMIC PACKAGE

CASE 620–10

P SUFFIX

PLASTIC PACKAGE

CASE 648–08

FN SUFFIX

PLCC

CASE 775–02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC10129L | Parallel-Load 8-Bit Shift Registers 16-CDIP -55 to 125 |

| MC10131FN | Parallel-Load 8-Bit Shift Registers 16-CDIP -55 to 125 |

| MC10131 | Parallel-Load 8-Bit Shift Registers 16-CFP -55 to 125 |

| MC10131L | Parallel-Load 8-Bit Shift Registers 16-CDIP -55 to 125 |

| MC10131P | Parallel-Load 8-Bit Shift Registers 16-CFP -55 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC1012P | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC10131FN | 制造商:ON Semiconductor 功能描述:Flip Flop D-Master-Slave Type Pos-Edge 1-Element 20-Pin PLLC Rail 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC10131FN WAF | 制造商:ON Semiconductor 功能描述: |

| MC10131FNR2 | 制造商:ON Semiconductor 功能描述:Flip Flop D-Master-Slave Type Pos-Edge 1-Element 20-Pin PLLC T/R 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC10131L | 制造商:ON Semiconductor 功能描述:Flip Flop D-Master-Slave Type Pos-Edge 1-Element 16-Pin CDIP Rail |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。