- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45197 > MB95F476HPMC1-G-SNE2 (FUJITSU LTD) MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | MB95F476HPMC1-G-SNE2 |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | MICROCONTROLLER, PQFP64 |

| 封裝: | 10 X10 MM, 1.70 MM HEIGHT, 0.50 MM PITCH, PLASTIC, LQFP-64 |

| 文件頁數(shù): | 22/76頁 |

| 文件大小: | 3707K |

| 代理商: | MB95F476HPMC1-G-SNE2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

MB95410H/470H Series

DS702-00004-0v01-E

29

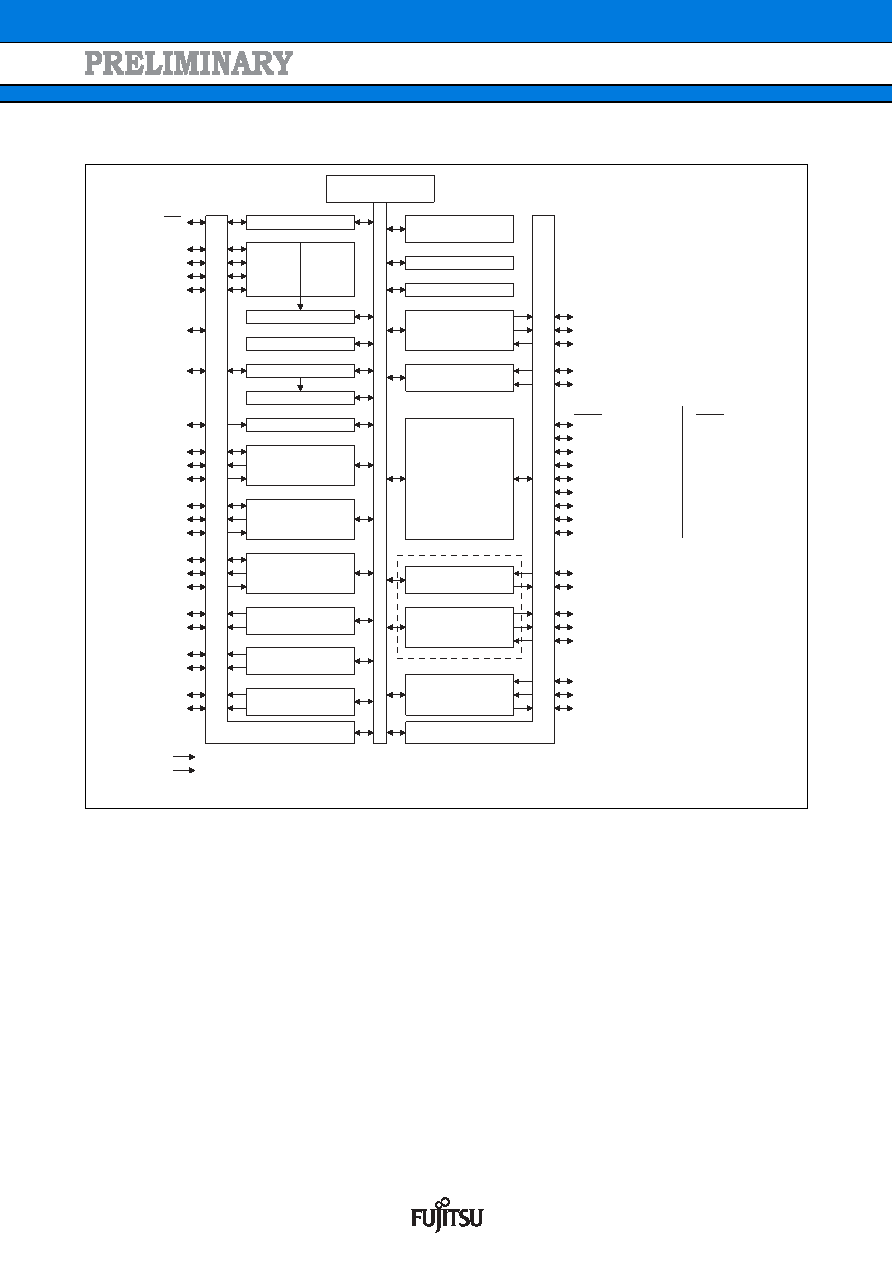

■ BLOCK DIAGRAM (MB95410H Series)

Reset with LVD

Flash with security function

(60/36/20 Kbyte)

F2MC-8FX CPU

RAM (2032/1008/496 bytes)

Interrupt controller

Oscillator

circuit

CR

oscillator

Clock control

On-chip debug

Wild register

Watch counter

External interrupt

UART/SIO ch. 0

8/16-bit composite timer ch. 0

8/10-bit A/D converter

16-bit reload timer

8/16-bit composite timer ch. 1

UART/SIO ch. 1

I2C

8/16-bit PPG ch. 0

8/16-bit PPG ch. 1

Port

PF2*1/RST*2

PF1/X1*2

PF0/X0*2

PG2/X1A*2

PG1/X0A*2

P00/INT00 to P07/INT07

C

P14/UCK0

P11/UO0

P10/UI0

P05/UCK1

P03/UO1

P04/UI1

UART/SIO ch. 2

P02/UCK2

P00/UO2

P01/UI2

P20/PPG00

P21/PPG01

P16/PPG10

P15/PPG11

P22/SCL*1

P23/SDA*1

P12*1/DBG

P52/TO00

P50/TO01

P51/EC0

P00/AN00 to P07/AN07

P13/ADTG

LCDC

(4 COM or 8 COM)

P90/V4 to P94/V0

PA0/COM0 to PA3/COM3

PB0/SEG00, PB1/SEG01

PC0/SEG02 to PC7/SEG09

P60/SEG10 to P67/SEG17

P43/SEG18 to P40/SEG21

PE0/SEG22 to PE7/SEG29

P07/SEG30 to P01/SEG36

PB2/SEG37 to PB4/SEG39

P90/V4 to P94/V0

4 COM:

8 COM:

PA0/COM0 to PA7/COM7

PB0/SEG00, PB1/SEG01

PC0/SEG02 to PC7/SEG09

P60/SEG10 to P67/SEG17

P43/SEG18 to P40/SEG21

PE0/SEG22 to PE7/SEG29

P07/SEG30 to P02/SEG35

PE5/TO11

PE6/TO10

PE7/EC1

Voltage comparator

P20/CMPN

P21/CMPP

P17/CMPO

P52/TI0

P53/TO0

Vcc

Vss

*1:

*2:

*3:

PF2, P12, P22 and P23 are N-ch open drain pins.

Software option

8/16-bit composite timer ch. 1 and 16-bit reload timer can be used as an event counter

when the event counter operating mode is enabled.

Inter

n

a

l

bu

s

*3

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。