- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45196 > MB95F168JPMC1 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | MB95F168JPMC1 |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 16.25 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.70 MM HEIGHT, 0.50 MM PITCH, PLASTIC, LFQFP-64 |

| 文件頁數(shù): | 51/76頁 |

| 文件大?。?/td> | 1492K |

| 代理商: | MB95F168JPMC1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當(dāng)前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

MB95160M Series

55

(Continued)

(VCC

= 5.0 V ± 10%, AVSS = VSS = 0.0 V, TA = 10 °C to + 85 °C)

*1 : R, C : Pull-up resistor and load capacitor of the SCL and SDA lines.

*2 :

Refer to “ (2) Source Clock/Machine Clock” for tMCLK.

m is CS4 bit and CS3 bit (bit 4 and bit 3) of I2C clock control register (ICCR) .

n is CS2 bit to CS0 bit (bit 2 to bit 0) of I2C clock control register (ICCR) .

Actual timing of I2C is determined by m and n values set by the machine clock (tMCLK) and CS4 to CS0 of

ICCR0 register.

Standard-mode :

m and n can be set at the range : 0.9 MHz < tMCLK (machine clock) < 10 MHz.

Setting of m and n determines the machine clock that can be used below.

(m, n)

= (1, 8)

: 0.9 MHz < tMCLK

≤ 1 MHz

(m, n)

= (1, 22) , (5, 4) , (6, 4) , (7, 4) , (8, 4) : 0.9 MHz < tMCLK ≤ 2 MHz

(m, n)

= (1, 38) , (5, 8) , (6, 8) , (7, 8) , (8, 8) : 0.9 MHz < tMCLK ≤ 4 MHz

(m, n)

= (1, 98)

: 0.9 MHz < tMCLK

≤ 10 MHz

Fast-mode :

m and n can be set at the range : 3.3 MHz < tMCLK (machine clock) < 10 MHz.

Setting of m and n determines the machine clock that can be used below.

(m, n)

= (1, 8)

: 3.3 MHz < tMCLK

≤ 4 MHz

(m, n)

= (1, 22) , (5, 4)

: 3.3 MHz < tMCLK

≤ 8 MHz

(m, n)

= (6, 4)

: 3.3 MHz < tMCLK

≤ 10 MHz

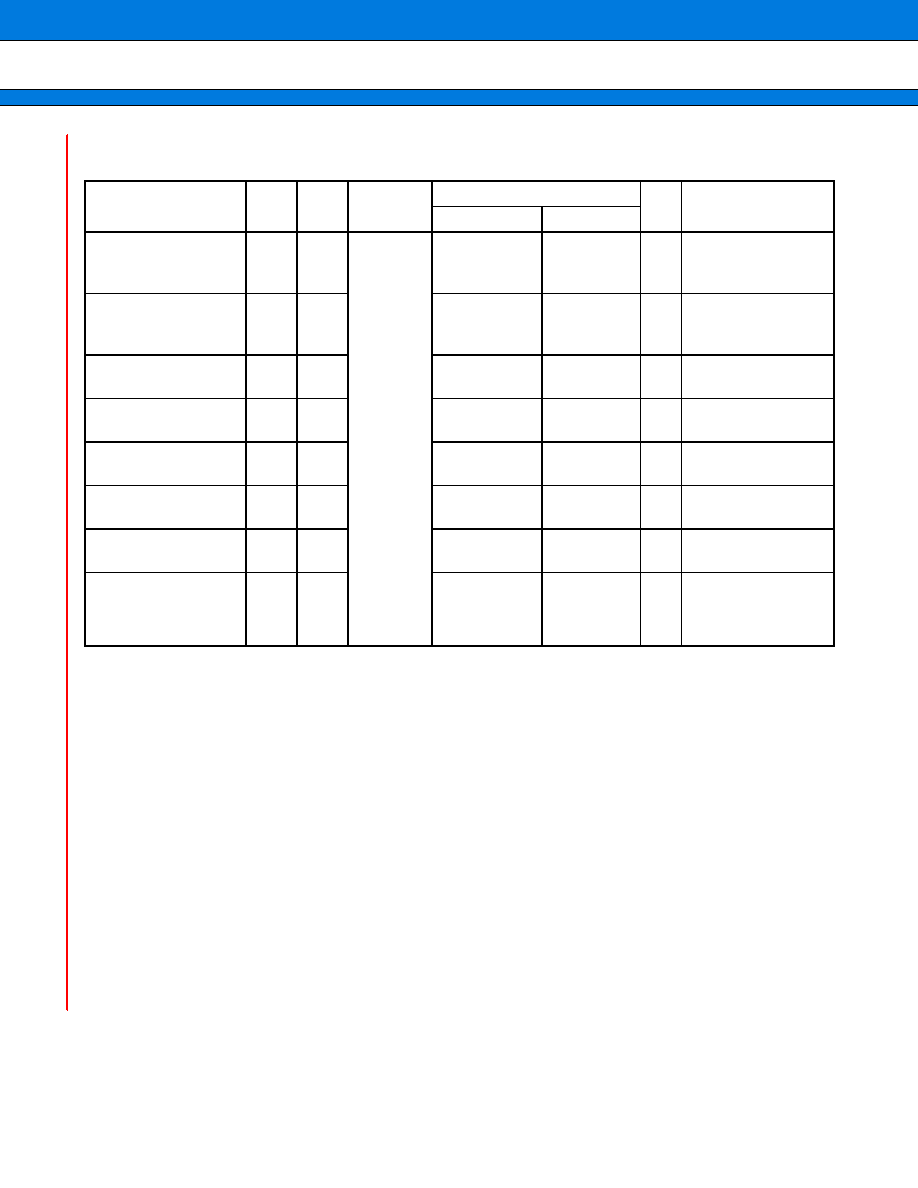

Parameter

Sym-

bol

Pin

name

Condi-

tions

Value*2

Unit

Remarks

Min

Max

Stop condition

detection

tSU;STO

SCL0

SDA0

R

= 1.7 k,

C

= 50 pF*1

2 tMCLK

20

ns

Undetected when 1

tMCLK is used at

reception

Restart condition

detection condition

tSU;STA

SCL0

SDA0

2 tMCLK

20

ns

Undetected when 1

tMCLK is used at

reception

Bus free time

tBUF

SCL0

SDA0

2 tMCLK

20

ns

At reception

Data hold time

tHD;DAT

SCL0

SDA0

2 tMCLK

20

ns

At slave transmission

mode

Data setup time

tSU;DAT

SCL0

SDA0

tLOW

3 tMCLK 20

ns

At slave transmission

mode

Data hold time

tHD;DAT

SCL0

SDA0

0

ns

At reception

Data setup time

tSU;DAT

SCL0

SDA0

tMCLK

20

ns

At reception

SDA

↓→SCL↑

(at wakeup function)

tWAKE-

UP

SCL0

SDA0

Oscillation

stabilization

wait time

+

2 tMCLK

20

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB95F204HP-G-SH-SNE2 | MICROCONTROLLER, PDIP24 |

| MB95F213HPF-G-SNE2 | MICROCONTROLLER, PDSO8 |

| MB95F204KP-G-SH-SNE2 | 8-BIT, FLASH, MICROCONTROLLER, PDIP24 |

| MB95F214HPH-G-SNE2 | MICROCONTROLLER, PDIP8 |

| MB95F202HP-G-SH-SNE2 | MICROCONTROLLER, PDIP24 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB95F168M | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Microcontroller |

| MB95F168MPMC | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Microcontroller |

| MB95F168MPMC1 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Microcontroller |

| MB95F168N | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Microcontroller |

| MB95F168NPMC | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。