- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377926 > MB90V540 (Fujitsu Limited) 16-bit Proprietary Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | MB90V540 |

| 廠商: | Fujitsu Limited |

| 英文描述: | 16-bit Proprietary Microcontroller |

| 中文描述: | 16位微控制器專有 |

| 文件頁(yè)數(shù): | 26/56頁(yè) |

| 文件大小: | 757K |

| 代理商: | MB90V540 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

MB90540/545 Series

26

I

CAN CONTROLLER

The MB90540 series contains two CAN controllers (CAN0 and CAN1), the MB90545 series contains only one

(CAN0). The Evaluation Chip MB90V540 also has two CAN controllers.

The CAN controller has the following features:

Conforms to CAN Specification Version 2.0 Part A and B

- Supports transmission/reception in standard frame and extended frame formats

Supports transmission of data frames by receiving remote frames

16 transmitting/receiving message buffers

- 29-bit ID and 8-byte data

- Multi-level message buffer configuration

Provides full-bit comparison, full-bit mask, acceptance register 0/acceptance register 1 for each message

buffer as 1D acceptance mask

- Two acceptance mask registers in either standard frame format or extended frame formats

Bit rate programmable from 10 Kbit/s to 1 Mbit/s (when input clock is at 16 MHz)

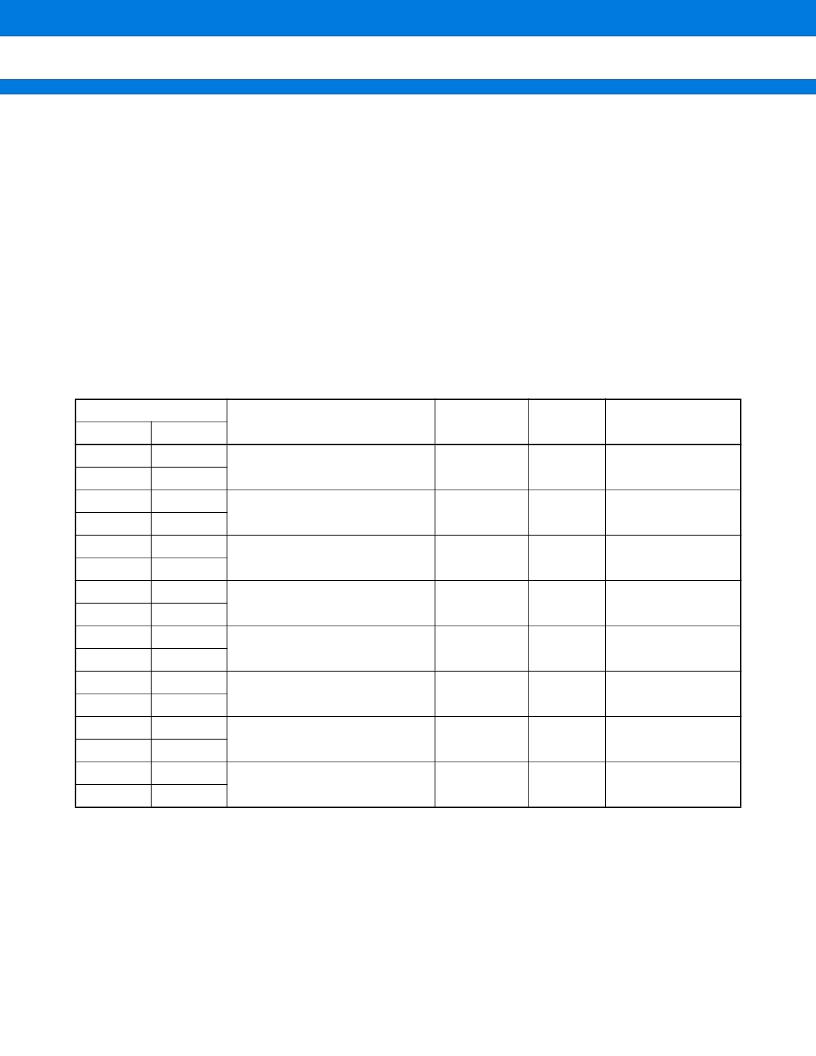

List of Control Registers

Address

Register

Abbreviation

Access

Initial Value

CAN0

CAN1

000070

H

000080

H

Message buffer valid register

BVALR

R/W

00000000 00000000

B

000071

H

000081

H

000072

H

000082

H

Transmit request register

TREQR

R/W

00000000 00000000

B

000073

H

000083

H

000074

H

000084

H

Transmit cancel register

TCANR

W

00000000 00000000

B

000075

H

000085

H

000076

H

000086

H

Transmit complete register

TCR

R/W

00000000 00000000

B

000077

H

000087

H

000078

H

000088

H

Receive complete register

RCR

R/W

00000000 00000000

B

000079

H

000089

H

00007A

H

00008A

H

Remote request receiving register

RRTRR

R/W

00000000 00000000

B

00007B

H

00008B

H

00007C

H

00008C

H

Receive overrun register

ROVRR

R/W

00000000 00000000

B

00007D

H

00008D

H

00007E

H

00008E

H

Receive interrupt enable register

RIER

R/W

00000000 00000000

B

00007F

H

00008F

H

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90V540CR | 16-bit Proprietary Microcontroller |

| MB90V540G | 16-bit Proprietary Microcontroller |

| MB90F549G | Octal Bus Transceivers And Registers With 3-State Outputs 24-CDIP -55 to 125 |

| MB90F549PF | 16-bit Proprietary Microcontroller |

| MB90F549PFV | 16-bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB-910 | 制造商:Circuit Test 功能描述:BREADBOARD WIRING KIT - 350 PCS |

| MB9100100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB9100-100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB91101 | 制造商:Panasonic Industrial Company 功能描述:IC |

| MB91101A | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:32-bit RISC Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。