- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377931 > MB90T673PFV (FUJITSU LTD) 16-Bit Bus Transceivers With 3-State Outputs 48-CFP -55 to 125 PDF資料下載

參數(shù)資料

| 型號(hào): | MB90T673PFV |

| 廠商: | FUJITSU LTD |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 16-Bit Bus Transceivers With 3-State Outputs 48-CFP -55 to 125 |

| 中文描述: | 16-BIT, 16 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | PLASTIC, LQFP-80 |

| 文件頁(yè)數(shù): | 41/124頁(yè) |

| 文件大小: | 2584K |

| 代理商: | MB90T673PFV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)

41

MB90670/675 Series

(2) N-ch Open-drain Port

Port 5 and port 9 are general-purpose I/O ports having a combined function as resource input/output. Each pin

can be switched between resource and port bitwise.

Only MB90675 series has port 9.

Operation as output port

When a data is written into the PDR register, the data is latched to the output latch of PDR. When the output

latch value is set to “0”, the output transistor is turned on and the pin status is put into an “L” level output, while

writing “1” turns off the transistor and put the pin in a high-impedance status.

If the output pin is pulled-up, setting output latch value to “1” puts the pin in the pull-up status.

Reading the PDR register returns the pin value (same as the output latch value in the PDR).

Note: Execution of a read-modify-write instruction (e.g. bit set instruction) reads out the output latch value rather

than the pin value, leaving output latch that is not manipulated unchanged.

Operation as input port

Setting corresponding bit of the PDR register to “1” turns off the output transistor and the pin is put into a high-

impedance status.

Reading the PDR register returns the pin level (“0” or “1”).

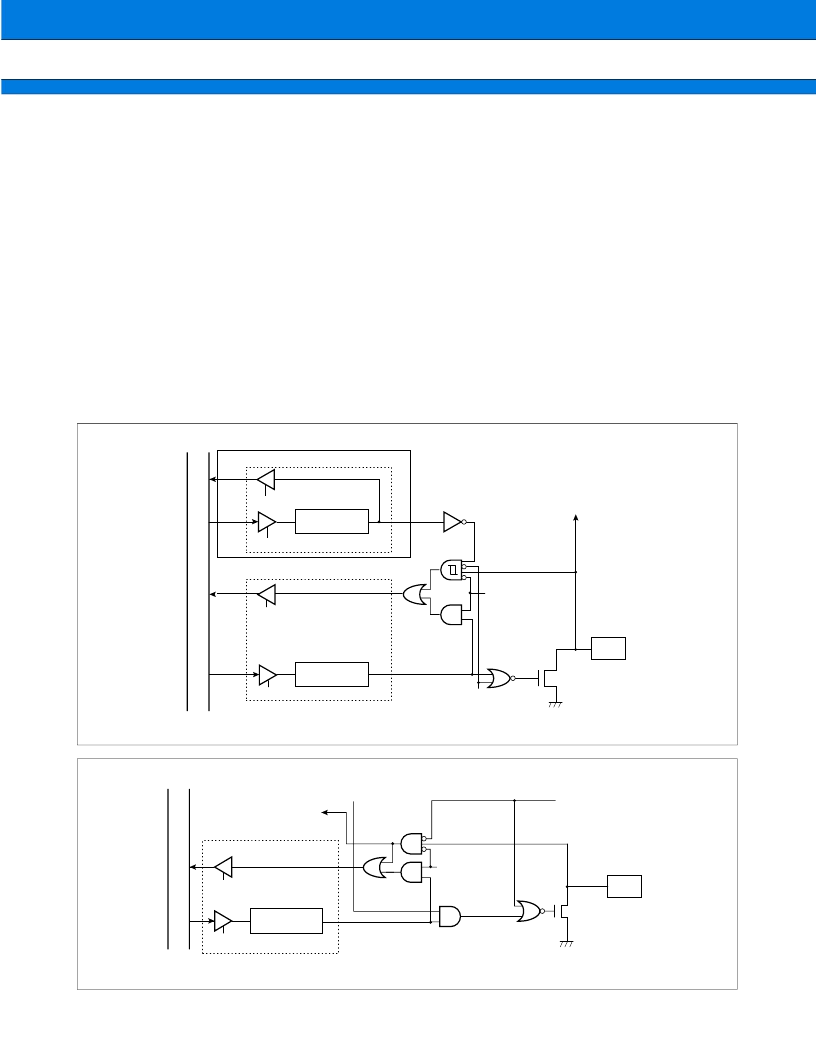

Block diagram of port 5

I

ADER (analog input enable register)

PDR (port data register)

ADER read

ADER write

ADER latch

PDR write

PDR read

Output latch

Standby control: Stop, timebase timer mode and SPL=1, or hardware standby mode

Standby control (SPL=1)

To analog input

Pin

Output trigger

RMW

(read-modify-write

instruction)

Block diagram of port 9

I

To resource input

PDR write

PDR read

Output latch

PDR (port data register)

From resource output

Output

trigger

Standby control: Stop, timebase timer mode and SPL=1, or hardware standby mode

Pin

RMW

(read-modify-

write instruc-

tion)

Standby control

(SPL=1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB90T678PF | 16-BIT BUFFERS/DRIVERS WITH 3-STATE OUTPUTS 48-CFP -55 to 125 |

| MB90T678PFV | 16-bit Proprietary Microcontroller |

| MB90P678PF | 16-bit Proprietary Microcontroller |

| MB90P678PFV | 16-Bit Bus Transceivers And Registers With 3-State Outputs 56-CFP -55 to 125 |

| MB90672PF | 16-bit Proprietary Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90V340A-102CR | 制造商:FUJITSU 功能描述: |

| MB-910 | 制造商:Circuit Test 功能描述:BREADBOARD WIRING KIT - 350 PCS |

| MB9100100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB9100-100 | 制造商:COM/DUO 功能描述:FAN 4-6WKS |

| MB91101 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。