- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377907 > MB89538APFM (FUJITSU LTD) 8-bit Original Microcontroller CMOS, F-2MC-8L MB89530A Series PDF資料下載

參數(shù)資料

| 型號(hào): | MB89538APFM |

| 廠商: | FUJITSU LTD |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-bit Original Microcontroller CMOS, F-2MC-8L MB89530A Series |

| 中文描述: | 8-BIT, MROM, 12.5 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | 12 X 12 MM, 1.70 MM HEIGHT, 0.65 MM PITCH, PLASTIC, QFP-64 |

| 文件頁(yè)數(shù): | 4/62頁(yè) |

| 文件大?。?/td> | 488K |

| 代理商: | MB89538APFM |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

MB89530A Series

4

(Continued)

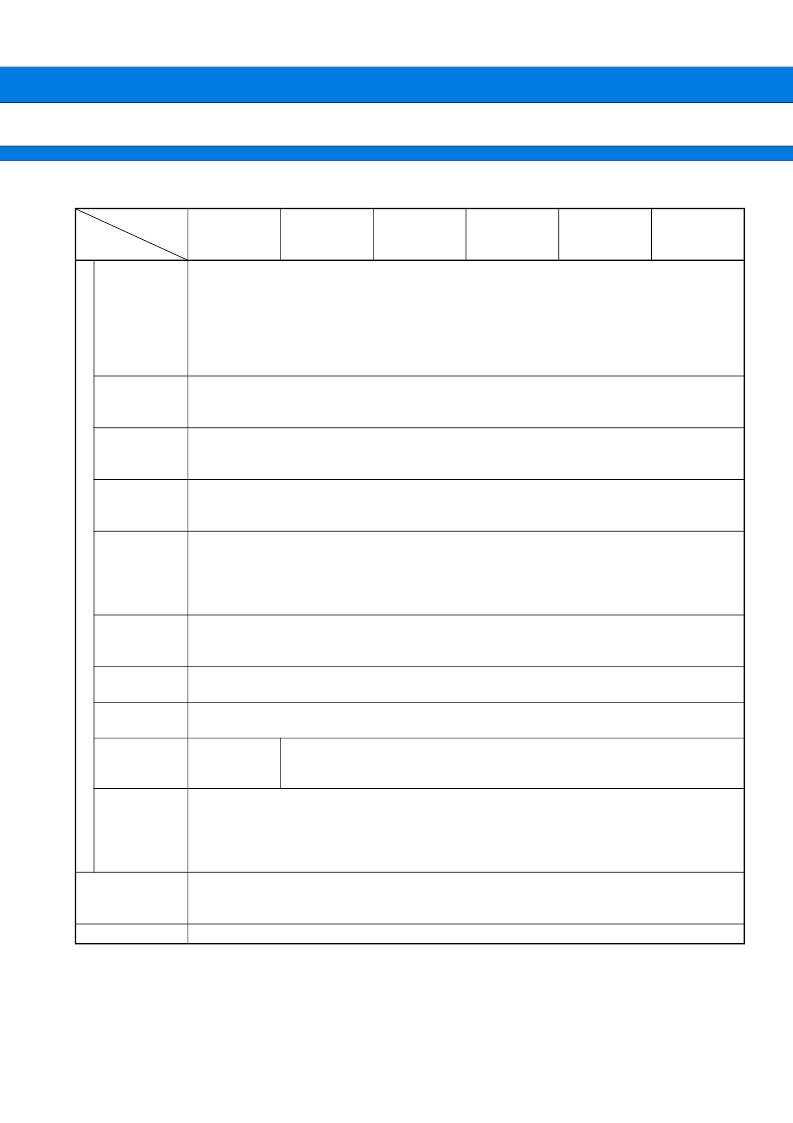

Part number

*1 : Depends on operating frequency.

*2 : Using external ROM and MBM27C512.

*3 : t

inst

represents instruction execution time. This can be selected as 1/4, 1/8, 1/16, 1/64 of the main clock cycle

or 1/2 of the sub clock cycle.

Note : MB89535A/537A/538A have no built-in I

2

C functions.

To use I

2

C functions, choose the MB89PV530/MB89P538/F538/537AC/538AC.

Parameter

MB89535A

MB89537A/

537AC

MB89538A/

538AC

MB89F538

MB89P538

MB89PV530

Pulse width

count timer

8-bit one-shot timer operation

(supports underflow output, operating clock period : 1, 4, 32 t

inst

*

3

, external)

8-bit reload timer operation

(supports square wave output, operating clock period : 1, 4, 32 t

inst

*

3

, external)

8-bit pulse width measurement operation

(continuous measurement, H width measurement, L width measurement,

↑

to

↑

,

↓

to

↓

, H

width measurement and

↑

to

↑

)

16-bit timer operation (operating clock period : 1 t

inst

*

3

, external)

16-bit event counter operation (select rising, falling, or both edges)

16-bit

×

1 ch

8 bit length

Selection of LSB first or MSB first

Transfer clock (2, 8, 32 t

inst

*

3

, external)

CLK synchronous/CLK asynchronous data transfer capability (8, 9 bit with parity bit, or 7,8 bit

without parity bit) .

Built-in baud rate generator provides selection of 14 baud rate settings.

CLK synchronous/CLK asynchronous data transfer capability (4, 6, 7, 8 bit with parity bit, or 5,

7, 8, 9 bit without parity bit) .

Built-in baud rate generator provides selection of 14 baud rate settings.

External clock output, 2-channel 8-bit PWM timer output also available for baud rate

settings.

Single-clock system : 4 channels independent, dual-clock system : 3 channels independent.

Selection of rising, falling, or both edge detection.

Can be used for recovery from standby mode (edge detection also available in stop mode)

Except MB89F538 : 8 ch, MB89F538 : 7 ch

Can be used for recovery from standby mode.

Can generate square wave signals with programmable period.

6-bit

×

1 channel or 12-bit

×

2 channels.

1-channel , compatible with Intel System Administrator bus version 1.0 and

Philips I

2

C specifications.

2-line communications

(

on MB89PV530

/

P538

/

F538/537AC

/

538AC

)

10-bit resolution

×

8 channels.

A/D conversion functions (conversion time : 60 t

inst

*

3

)

Supports repeated calls from external clock (except MB89F538) .

Supports repeated calls from internal clock.

Standard voltage input provided (AVR)

16-bit timer/

counter

Serial I/O

UART/SIO

UART

External

interrupt 1

External

interrupt 2

6-bit PPG,

12-bit PPG

I

2

C bus

interface

A/D converter

Standby modes

(power saving

modes)

Process

Sleep mode, stop mode, sub clock mode, watch mode.

CMOS

P

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB89538APFV | 8-bit Original Microcontroller CMOS, F-2MC-8L MB89530A Series |

| MB89538HP | 8-bit Original Microcontroller CMOS |

| MB89538HPF | 8-bit Original Microcontroller CMOS |

| MB89538HPFM | 8-bit Original Microcontroller CMOS |

| MB89538HPFV | 8-bit Original Microcontroller CMOS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB89538APFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Original Microcontroller CMOS, F-2MC-8L MB89530A Series |

| MB89538C | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Original Microcontroller |

| MB89538CP | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Original Microcontroller |

| MB89538CPF | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Original Microcontroller |

| MB89538CPFM | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit Original Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。