- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377881 > MB40C318PFV (FUJITSU LTD) 8-bit 140 MSPS A/D Converter PDF資料下載

參數(shù)資料

| 型號: | MB40C318PFV |

| 廠商: | FUJITSU LTD |

| 元件分類: | ADC |

| 英文描述: | 8-bit 140 MSPS A/D Converter |

| 中文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP48 |

| 封裝: | 7 X 7 MM, 0.50 MM PITCH, PLASTIC, LQFP-48 |

| 文件頁數(shù): | 3/16頁 |

| 文件大小: | 173K |

| 代理商: | MB40C318PFV |

3

MB40C318

I

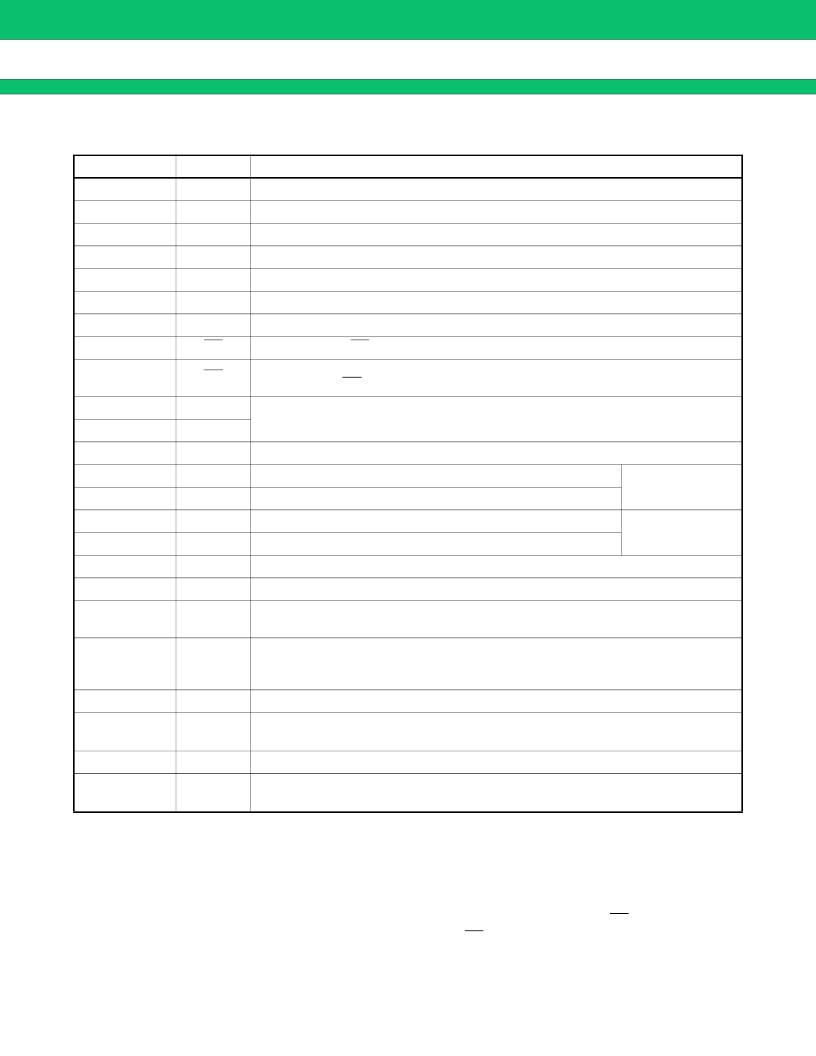

PIN DESCRIPTION

The values in parentheses are standard.

I

PRECAUTIONS ON USE

Be sure to ground the pins of AV

DD

, DV

DD

, DV

DDI

, V

RT

, V

RB

, V

R1

, V

R2

, and V

R3

via high-frequency capacitor.

Place the high-frequency capacitor as close as possible to the pin.

To avoid generation of undesired current owing to indetermination of internal logic, set CE to “H” at powering

on and input more than five clock pulses just after operation (CE: “H”

→

“L”).

Pin No.

Symbol

Description

3, 9, 13, 45

AV

DD

Analog power supply (+3.3 V)

16, 43

DV

DD

Digital power supply (+3.3 V)

27

DV

DDI

Digital power supply for CLKEP/CLKEN (+5.0 V or +3.3 V)

4, 7, 12, 44

AV

SS

Analog power supply ground pin (0 V)

18, 41

DV

SS

Digital power supply ground pin (0 V)

33 to 40

D

A7

to D

A0

Digital output pin (Port A) D

A7

: MSB, D

A0

: LSB

19 to 26

D

B7

to D

B0

Digital output pin (Port B) D

B7

: MSB, D

B0

: LSB

11

CE

Power down at CE input “H” (internal pull-up resistor)

14

OE

Digital output (Both Port A, B) and clock output (CLKOA, CLKOB) are high

impedance at OE input “H”.

10

CKSEL

Mode of operation setting input pin (Refer to

I

MODE SETTING)

15

DSEL

28

RESET

Dividing circuit reset input pin (See

I

TIMING CHART 2, 3)

29

CLKEP

Differential clock (positive-phase) input pin (max 140 MHz)

PECL level

32

CLKEN

Differential clock (negative-phase) input pin (max 140 MHz)

31

CLKA

Two-phase clock (A ch) input pin (max 70 MHz)

CMOS level

30

CLKB

Two-phase clock (B ch) input pin (max 70 MHz)

42

CLKOA

Clock output pin (See

I

TIMING CHART 1 to 4)

17

CLKOB

Clock output pin (See

I

TIMING CHART 1 to 4)

8

V

INA

Analog input pin

Input range is V

RT

to V

RB

(0 V to 3.0 V: 2 Vp-p)

Reference 1/4 voltage output pin (Add 0.1

μ

F for AV

SS

)

Reference 1/2 voltage output pin (Add 0.1

μ

F for AV

SS

)

Reference 3/4 voltage output pin (Add 0.1

μ

F for AV

SS

)

Reference voltage input pin on top side

2

1

48

V

R1

V

R2

V

R3

46

V

RT

47

V

REFT

Reference voltage output pin

By connecting to V

RT

, 0.9

×

AV

DD

(..

Reference voltage input pin on bottom side

6

V

RB

5

V

REFB

Reference voltage output pin

By connecting to V

RB

, 0.3

×

AV

DD

(..

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB40C328V | 8-bit 100 MSPS A/D Converter |

| MB40C328VPFV | 8-bit 100 MSPS A/D Converter |

| MB40C328 | 8-bit 100 MSPS A/D Converter |

| MB40C328PFV | 8-bit 100 MSPS A/D Converter |

| MB40C338 | 3 ch 8-bit 162 MSPS A/D Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB40C318V | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit 140 MSPS A/D Converter |

| MB40C318VPFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit 140 MSPS A/D Converter |

| MB40C328 | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit 100 MSPS A/D Converter |

| MB40C328PFV | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit 100 MSPS A/D Converter |

| MB40C328V | 制造商:FUJITSU 制造商全稱:Fujitsu Component Limited. 功能描述:8-bit 100 MSPS A/D Converter |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。