-

[北京]010-87982920

-

[深圳]0755-82701186

- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67809 > MAX6721AUTTZD3+T (MAXIM INTEGRATED PRODUCTS INC) Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits PDF資料下載

參數(shù)資料

| 型號: | MAX6721AUTTZD3+T |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| 中文描述: | 2-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO6 |

| 封裝: | ROHS COMPLIANT, SOT-23, 6 PIN |

| 文件頁數(shù): | 12/18頁 |

| 文件大小: | 186K |

| 代理商: | MAX6721AUTTZD3+T |

MAX6715A–MAX6729A/MAX6797A

Dual/Triple, Ultra-Low-Voltage, SOT23 P

Supervisory Circuits

_

__

_

3

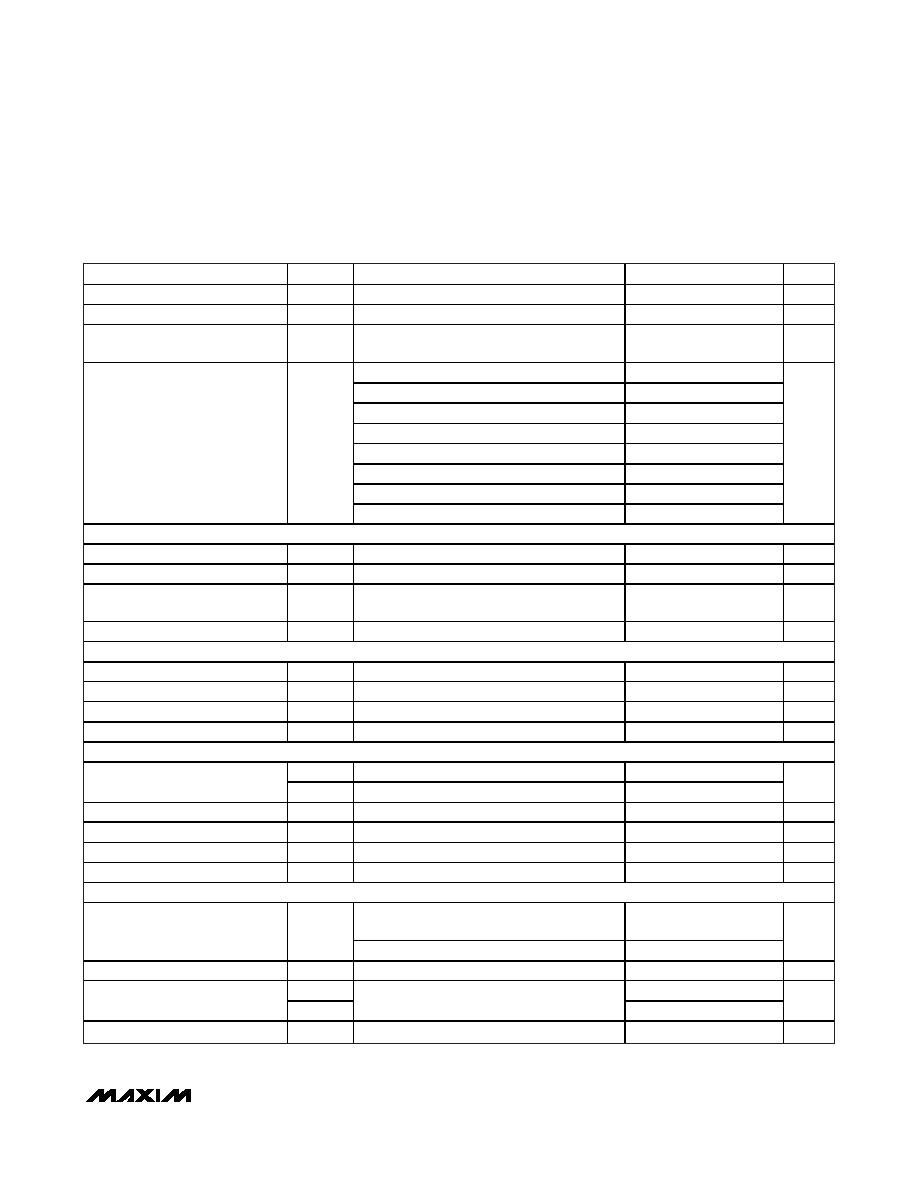

ELECTRICAL CHARACTERISTICS (continued)

(VCC1 = 0.8V to 5.5V, VCC2 = 0.8V to 5.5V, GND = 0V, TA = -40°C to +125°C, unless otherwise noted. Typical values are at TA =

+25°C.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Reset Threshold Tempco

ΔVTH/°C

20

ppm/°C

Reset Threshold Hysteresis

VHYST

Referenced to VTH typical

0.5

%

VCC to Reset Output Delay

tRD

VCC1 = (VTH1+ 100mV) to (VTH1 - 100mV) or

VCC2 = (VTH2 + 75mV) to (VTH2 - 75mV)

20

s

D1

1.1

1.65

2.2

D2

8.8

13.2

17.6

D7 (MAX6797A only)

17.5

26.25

35

D8 (MAX6797A only)

35

52.5

70

D3

140

210

280

D5

280

420

560

D6

560

840

1120

Reset Timeout Period

tRP

D4

1120

1680

2240

ms

ADJUSTABLE RESET COMPARATOR INPUT (MAX6719A/MAX6720A/MAX6723A–MAX6727A)

RSTIN Input Threshold

VRSTIN

611

626.5

642

mV

RSTIN Input Current

IRSTIN

-100

+100

nA

RSTIN Hysteresis

3mV

RSTIN to Reset Output Delay

tRSTIND

VRSTIN to (VRSTIN - 30mV)

22

s

POWER-FAIL INPUT (MAX6728A/MAX6729A)

PFI Input Threshold

VPFI

611

626.5

642

mV

PFI Input Current

IPFI

-100

+100

nA

PFI Hysteresis

VPFH

3mV

PFI to PFO Delay

tDPF

(VPFI + 30mV) to (VPFI - 30mV)

2

s

MANUAL-RESET INPUT (MAX6715A–MAX6722A/MAX6725A–MAX6729A)

VIL

0.3

VCC1

MR Input Voltage

VIH

0.7

VCC1

V

MR Minimum Pulse Width

1s

MR Glitch Rejection

100

ns

MR to Reset Delay

tMR

200

ns

MR Pullup Resistance

25

50

80

k

Ω

WATCHDOG INPUT (MAX6721A–MAX6729A)

First watchdog period after reset timeout

period

35

54

72

Watchdog Timeout Period

tWD

Normal mode

1.12

1.68

2.24

s

WDI Pulse Width

tWDI

(Note 2)

50

ns

VIL

0.3

VCC1

WDI Input Voltage

VIH

0.7

VCC1

V

WDI Input Current

IWDI

WDI = 0V or VCC1-1

+1

A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX6721AUTTZD4+T | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| MAX6721AUTTZD5+T | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| MAX6721AUTTZD6+T | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| MAX6721AUTVDD3+T | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

| MAX6721AUTVFD1+T | Dual/Triple Ultra-Low-Voltage SOT23 µP Supervisory Circuits |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX6721AUTTZD4+T | 功能描述:監(jiān)控電路 RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| MAX6721AUTTZD5+T | 功能描述:監(jiān)控電路 Dual uPower Supervisor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| MAX6721AUTTZD6+T | 功能描述:監(jiān)控電路 Dual uPower Supervisor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| MAX6721AUTVDD1+T | 功能描述:監(jiān)控電路 Dual uPower Supervisor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| MAX6721AUTVDD2+T | 功能描述:監(jiān)控電路 Dual uPower Supervisor RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。

- VIP會員服務(wù) |

- 廣告服務(wù) |

- 付款方式 |

- 聯(lián)系我們 |

- 招聘銷售 |

- 免責(zé)條款 |

- 網(wǎng)站地圖