- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383308 > MAX1003CAX (MAXIM INTEGRATED PRODUCTS INC) Low-Power, 90Msps, Dual 6-Bit ADC PDF資料下載

參數(shù)資料

| 型號(hào): | MAX1003CAX |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類(lèi): | ADC |

| 英文描述: | Low-Power, 90Msps, Dual 6-Bit ADC |

| 中文描述: | DUAL 1-CH 6-BIT FLASH METHOD ADC, PARALLEL ACCESS, PDSO36 |

| 封裝: | 0.300 INCH, 0.80 MM PITCH, SSOP-36 |

| 文件頁(yè)數(shù): | 3/12頁(yè) |

| 文件大?。?/td> | 115K |

| 代理商: | MAX1003CAX |

M

Low-Power, 90Msps, Dual 6-Bit ADC

_______________________________________________________________________________________

3

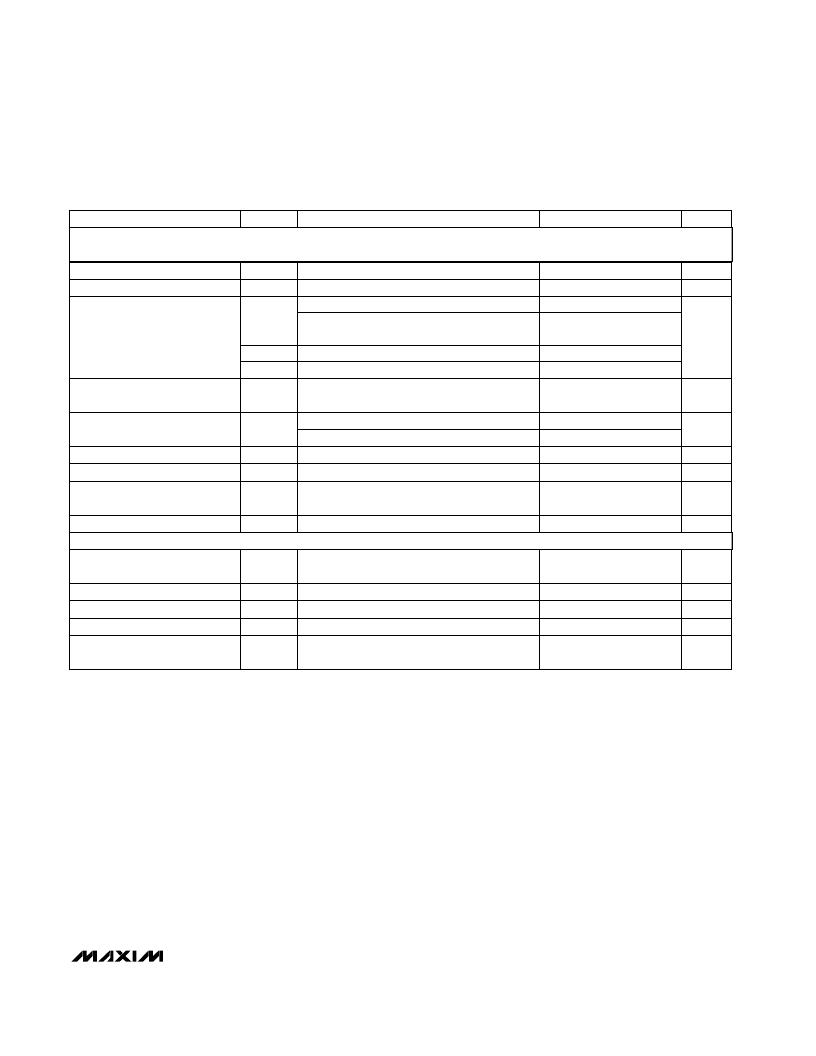

AC ELECTRICAL CHARACTERISTICS

(V

CC

= +5V ±5%, V

CCO

= 3.3V ±300mV, T

A

= +25°C, unless otherwise noted.)

Note 1:

Best-fit straight-line linearity method.

Note 2:

A typical application will AC couple the analog input to the DC bias level present at the analog inputs (typically 2.35V).

However, it is also possible to DC couple the analog input (using differential or single-ended drive) within this common-

mode input range (Figures 4 and 5).

Note 3:

PSRR is defined as the change in the mid-gain full-scale range as a function of the variation in V

CC

supply voltage,

expressed in decibels.

Note 4:

The current in the V

CCO

supply is a strong function of the capacitive loading on the digital outputs. To minimize supply tran-

sients and achieve optimal dynamic performance, reduce the capacitive-loading effects by keeping line lengths on the dig-

ital outputs to a minimum.

Note 5:

Offset-correction compensation enabled, 0.22μF at Q and I compensation inputs (Figures 2 and 3).

Note 6:

t

PD

and t

SKEW

are measured from the 1.4V level of the output clock, to the 1.4V level of either the rising or falling edge of a

data bit. t

DCLK

is measured from the 50% level of the clock-overdrive signal on TNK+ to the 1.4V level of DCLK. The capac-

itive load on the outputs is 15pF.

GAIN = GND, open, V

CC

GAIN = open (mid gain)

GAIN = open (mid gain), f

IN

= 50MHz,

-1dB below full scale

GAIN = V

CC

(high gain)

5.7

ENOB

M

5.6

5.85

Effective Number of Bits

GAIN = open (mid gain)

GAIN = GND (low gain)

Q channel

I channel

dB

LSB

CONDITIONS

MHz

55

BW

Analog Input -0.5dB Bandwidth

Msps

90

f

MAX

Maximum Sample Rate

-55

±0.25

XTLK

OMM

Crosstalk Between ADCs

Offset Mismatch Between ADCs

LSB

-0.5

0.5

OFF

Input Offset (Note 5)

-0.5

0.5

dB

35.5

37

SINAD

Signal-to-Noise plus Distortion

Ratio

Bits

5.85

ENOB

L

5.8

ENOB

H

(Note 5)

dB

-0.2

±0.1

0.2

AM

Amplitude Match Between

ADCs

-0.5

0.5

(Note 6)

TNK+ to DCLK (Note 6)

Figure 8

(Note 6)

ns

ns

ns

1.5

5.3

7.5

t

SKEW

t

DCLK

t

AD

Data Valid Skew

Input to DCLK Delay

Aperture Delay

ns

3.6

t

PD

Clock to Data Propagation

Delay

degrees

-2

±0.5

2

PM

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

Phase Match Between ADCs

TIMING CHARACTERISTICS

(Data outputs: R

L

= 1M

, C

L

= 15pF)

Figure 8

clock

cycle

1

PD

Pipeline Delay

DYNAMIC PERFORMANCE

(Gain = open, external 90MHz clock (Figure 7), V

INI

= V

INQ

= 20MHz sine, amplitude -1dB below

full scale, unless otherwise noted.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX1005 | IF Undersampler |

| MAX1005CEE | IF Undersampler |

| MAX1005EEE | IF Undersampler |

| MAX101 | 500Msps, 8-Bit ADC with Track/Hold |

| MAX101CFR | 500Msps, 8-Bit ADC with Track/Hold |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX1003CAX+ | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Low-Power 90Msps Dual 6-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1003CAX+T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC Low-Power 90Msps Dual 6-Bit RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1003CAX-T | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類(lèi)型:Differential 信噪比:107 dB 接口類(lèi)型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| MAX1003EVKIT | 功能描述:數(shù)據(jù)轉(zhuǎn)換 IC 開(kāi)發(fā)工具 RoHS:否 制造商:Texas Instruments 產(chǎn)品:Demonstration Kits 類(lèi)型:ADC 工具用于評(píng)估:ADS130E08 接口類(lèi)型:SPI 工作電源電壓:- 6 V to + 6 V |

| MAX1005 | 制造商:MAXIM 制造商全稱(chēng):Maxim Integrated Products 功能描述:IF Undersampler |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。