- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25619 > MAC7141VFU50 (FREESCALE SEMICONDUCTOR INC) 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | MAC7141VFU50 |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP100 |

| 封裝: | 14 X 14 MM, 0.50 MM PITCH, LQFP-100 |

| 文件頁(yè)數(shù): | 11/56頁(yè) |

| 文件大小: | 1216K |

| 代理商: | MAC7141VFU50 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)

ElectricalCharacteristics

MAC7100 Microcontroller Family Hardware Specifications, Rev. 1.2

Preliminary

Freescale Semiconductor

19

3.8.6

Startup

Table 23 summarizes several startup characteristics. Refer to Section 4.3.6.10, “CRG Operating Mode

Details,” in the MAC7100 Microcontroller Family Reference Manual (MAC7100RM) for details.

3.8.6.1

Power On and Low Voltage Reset (POR and LVR)

The VPORR and VPORA levels are derived from VDD2.5. The VLVRA level is derived from VDD2.5. They

are also valid if the device is powered externally. After releasing a POR or LVR reset, the oscillator and

clock quality checks start. After tCQOUT (Table 19, J4) if no valid oscillation is detected, the MCU will

start using the internal self-generated clock. The minimum startup time is given by tuposc (Table 19, J3).

3.8.6.2

SRAM Data Retention

SRAM content integrity is guaranteed if the CRGFLG[PORF] bit is not set following a reset operation.

3.8.6.3

External Reset

When external reset is asserted for a time greater than PWRSTL, the CRG generates an internal reset and

the CPU fetches the reset vector without a clock quality check, if there was stable oscillation before reset.

3.8.6.4

Stop Recovery

The MCU can return from stop to run mode in response to an external interrupt or an API. Two delays

occur before the MCU resumes execution. First, the voltage regulator must exit reduced power mode and

return to full performance mode (this assumes that the internal regulator is used rather than driving VDD2.5

and VDDPLL with an external regulator). Second, a clock quality check is performed in the same manner

as for a power-on reset before releasing the clocks to the system.

3.8.6.5

Pseudo Stop Recovery

Recovery from pseudo stop mode is similar to stop mode in that the VREG must return to FPM, but since

the oscillator is not stopped there is no delay for clock stabilization. The MCU is returned to run mode by

internal or external interrupts.

3.8.6.6

Doze Recovery

Recovery from doze mode avoids both the VREG and oscillator recovery periods. The MCU is returned

to run mode by internal or external interrupts.

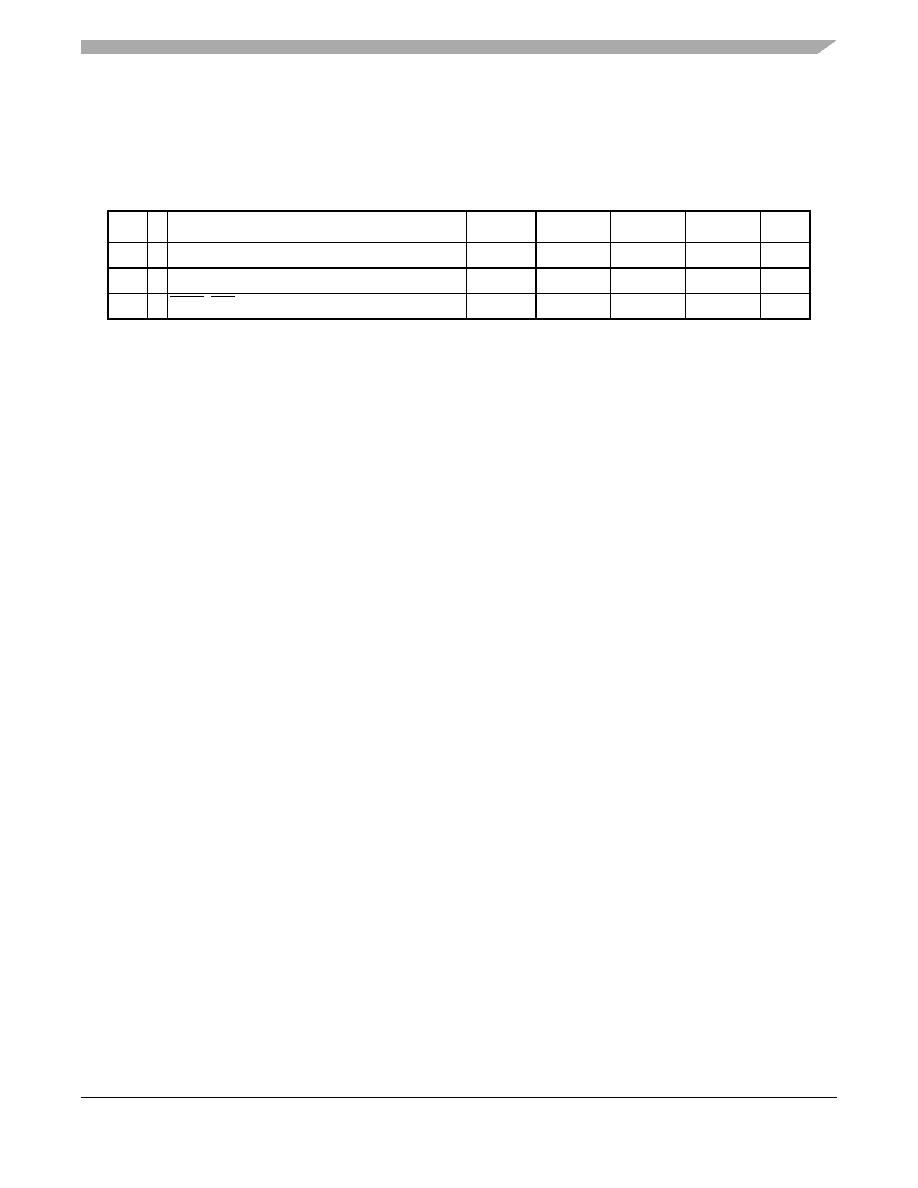

Table 23. CRG Startup Characteristics

Num C

Rating

Symbol

Min

Typ

Max

Unit

L1

D Reset input pulse width

PWRSTL

2—

—

tOSC

L2

D Startup from Reset

nRST

192

—

196

tOSC

L3

D XIRQ, IRQ pulse width, edge-sensitive mode

PWIRQ

20

—

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC7116MPV50 | 32-BIT, FLASH, 50 MHz, MICROCONTROLLER, PQFP144 |

| MAC7116VAG50R2 | 32-BIT, FLASH, 50 MHz, RISC MICROCONTROLLER, PQFP144 |

| MAC7121VAG40 | 32-BIT, FLASH, 40 MHz, RISC MICROCONTROLLER, PQFP112 |

| MAX9380ESA+ | 2 LINE TO 1 LINE MULTIPLEXER, COMPLEMENTARY OUTPUT, PDSO8 |

| MB2052BB-T | MB SERIES, DUAL 8-BIT REGISTERED TRANSCEIVER, TRUE OUTPUT, PQFP52 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAC7141VPV | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MAC7100 Microcontroller Family Hardware Specifications |

| MAC7141VPV50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7141VVF | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MAC7100 Microcontroller Family Hardware Specifications |

| MAC7141VVF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7141VVM50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。