- 您現在的位置:買賣IC網 > PDF目錄370998 > MAC7121CVF (Motorola, Inc.) MAC7100 Microcontroller Family Hardware Specifications PDF資料下載

參數資料

| 型號: | MAC7121CVF |

| 廠商: | Motorola, Inc. |

| 英文描述: | MAC7100 Microcontroller Family Hardware Specifications |

| 中文描述: | MAC7100微控制器系列硬件規(guī)格 |

| 文件頁數: | 18/48頁 |

| 文件大小: | 1514K |

| 代理商: | MAC7121CVF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

18

MAC7100 Microcontroller Family Hardware Specifications

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Electrical Characteristics

3.8.6

Startup

Table 21 summarizes several startup characteristics explained in this section. Refer to the

MAC7100

Microcontroller Family Reference Manual

(MAC7100RM/D) for a detailed description of the startup

behavior.

3.8.6.1

Power On and Low Voltage Reset (POR and LVR)

The release level V

PORR

and the assert level V

PORA

are derived from the V

DD

2.5 supply. The assert level

V

LVRA

is derived from the V

DD

2.5 supply. They are also valid if the device is powered externally. After

releasing the POR or LVR reset, the oscillator and the clock quality check are started. If after a time t

CQOUT

no valid oscillation is detected, the MCU will start using the internal self-generated clock. The fastest startup

time possible is given by t

uposc

(refer to Table 17).

3.8.6.2

SRAM Data Retention

The SRAM contents integrity is guaranteed if the PORF bit in the CRGFLG register is not set following a

reset operation.

3.8.6.3

External Reset

When external reset is asserted for a time greater than PW

RSTL

, the CRG module generates an internal reset

and the CPU starts fetching the reset vector without doing a clock quality check, if there was stable

oscillation before reset.

3.8.6.4

Stop Recovery

The MCU can be returned to run mode from the stop mode by an external interrupt. A clock quality check

is performed in the same manner as for POR before releasing the clocks to the system.

3.8.6.5

Pseudo Stop and Doze Recovery

Recovery from pseudo stop and doze modes are essentially the same, since the oscillator is not stopped in

either mode. The controller is returned to run mode by internal or external interrupts or other wakeup events

in the system. After t

wrs

, the CPU fetches an interrupt vector if the wakeup event was an interrupt, or

continues to execute code if the wakeup event was not an interrupt.

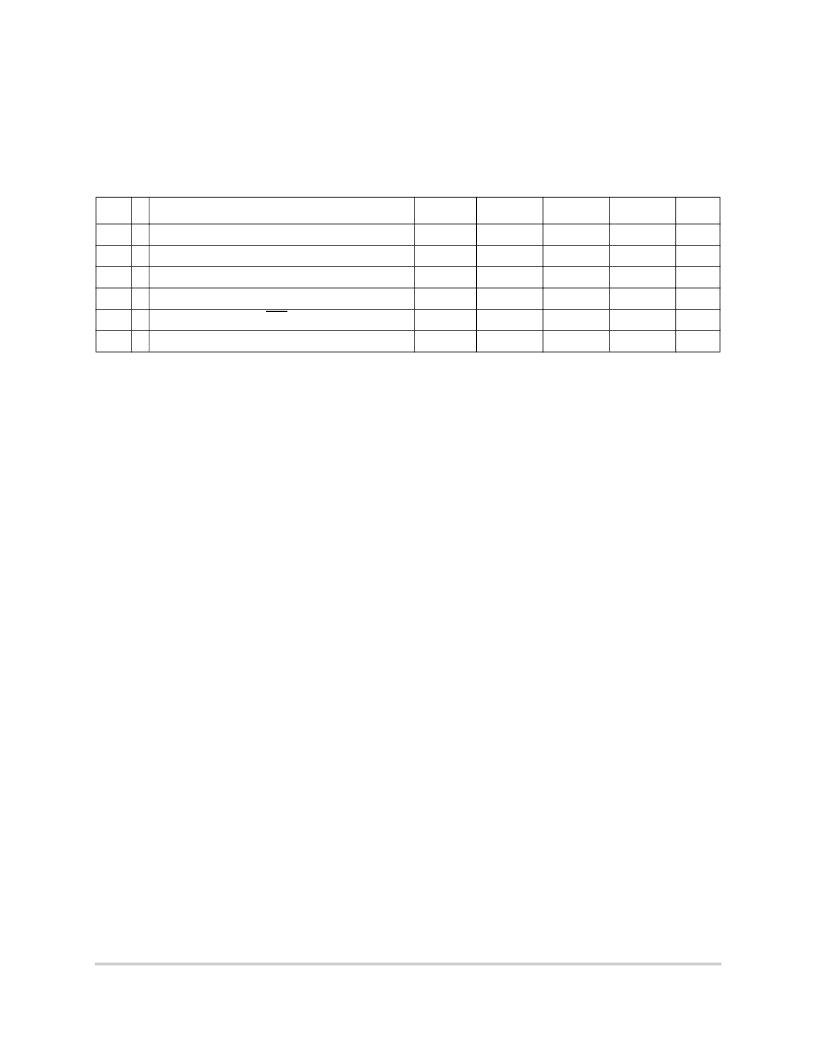

Table 21. CRG Startup Characteristics

Num C

Rating

Symbol

Min

Typ

Max

Unit

K1

T POR release level

V

PORR

V

PORA

PW

RSTL

n

RST

PW

IRQ

t

WRS

—

—

2.07

V

K2

T POR assert level

0.97

—

—

V

K3

D Reset input pulse width, minimum input time

2

—

—

t

osc

n

osc

ns

K4

D Startup from Reset

192

—

196

K5

D Interrupt pulse width, IRQ edge-sensitive mode

20

—

—

K6

D Wait recovery startup time

—

—

14

t

cyc

F

Freescale Semiconductor, Inc.

n

.

相關PDF資料 |

PDF描述 |

|---|---|

| MAC7131 | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7131CFU | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7131CPV | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7131CVF | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7131MFU | MAC7100 Microcontroller Family Hardware Specifications |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MAC7121CVF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7121CVM50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7121MAF50 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Hardware Specifications |

| MAC7121MAG40 | 功能描述:ARM微控制器 - MCU MAC7121 NO BUS 16CH A/D RoHS:否 制造商:STMicroelectronics 核心:ARM Cortex M4F 處理器系列:STM32F373xx 數據總線寬度:32 bit 最大時鐘頻率:72 MHz 程序存儲器大小:256 KB 數據 RAM 大小:32 KB 片上 ADC:Yes 工作電源電壓:1.65 V to 3.6 V, 2 V to 3.6 V, 2.2 V to 3.6 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:LQFP-48 安裝風格:SMD/SMT |

| MAC7121MAG50 | 制造商:Freescale Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。