- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370997 > MAC7100 (Motorola, Inc.) MAC7100 Microcontroller Family Hardware Specifications PDF資料下載

參數(shù)資料

| 型號: | MAC7100 |

| 廠商: | Motorola, Inc. |

| 英文描述: | MAC7100 Microcontroller Family Hardware Specifications |

| 中文描述: | MAC7100微控制器系列硬件規(guī)格 |

| 文件頁數(shù): | 14/48頁 |

| 文件大小: | 1514K |

| 代理商: | MAC7100 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁

14

MAC7100 Microcontroller Family Hardware Specifications

PRELIMINARY—SUBJECT TO CHANGE WITHOUT NOTICE

For More Information On This Product,

Go to: www.freescale.com

MOTOROLA

Electrical Characteristics

3.8

Clock and Reset Generator Electrical

Characteristics

This section describes the electrical characteristics for the oscillator, phase-locked loop, clock monitor and

reset generator.

3.8.1

Oscillator Characteristics

The MAC7100 Family features an internal low power loop controlled Pierce oscillator and a full swing Pierce

oscillator/external clock mode. The selection of loop controlled Pierce oscillator or full swing Pierce

oscillator/external clock depends on the level of the XCLKS signal at the rising edge of the RESET signal.

Before asserting the oscillator to the internal system clock distribution subsystem, the quality of the

oscillation is checked for each start from either power on, STOP or oscillator fail. t

CQOUT

specifies the

maximum time before switching to the internal self clock mode after POR or STOP if a proper oscillation is

not detected. The quality check also determines the minimum oscillator start-up time t

UPOSC

. The device also

features a clock monitor. A Clock Monitor Failure is asserted if the frequency of the incoming clock signal

is below the Clock Monitor Assert Frequency f

CMFA

.

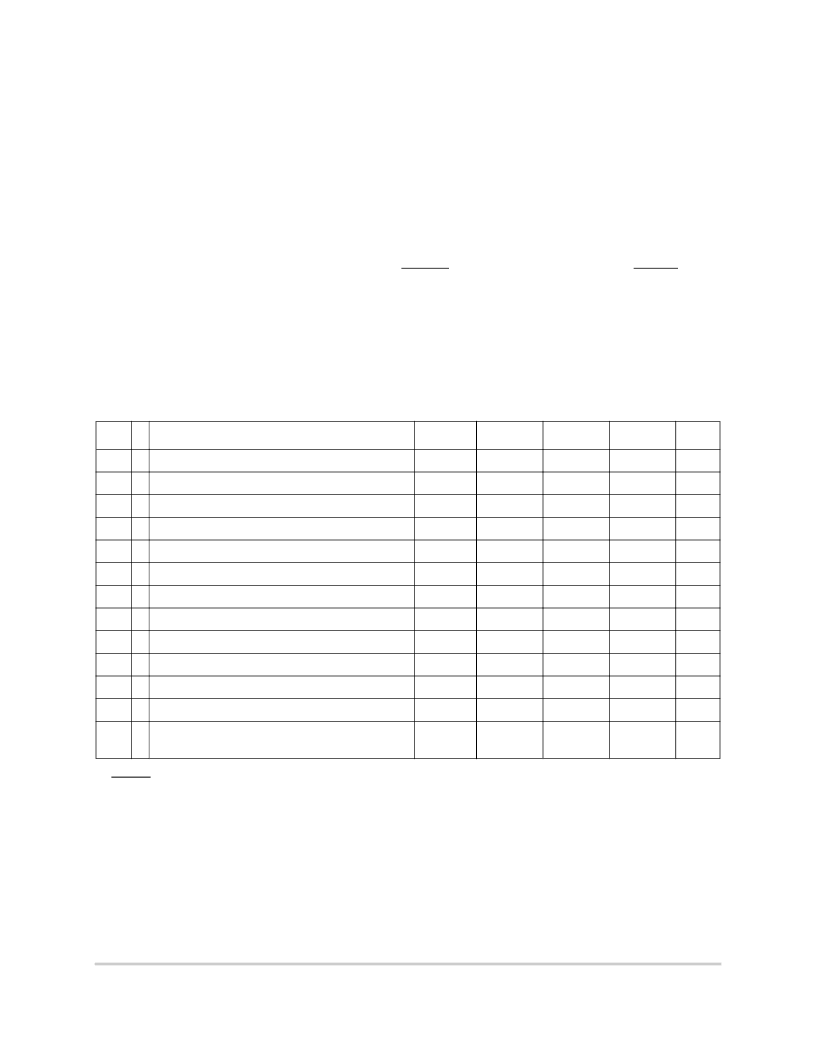

Table 17. Oscillator Characteristics

Num C

Rating

Symbol

Min

Typ

Max

Unit

H1a

C Crystal oscillator range (loop controlled Pierce)

f

OSC

4.0

—

16

MHz

H1b

C Crystal oscillator range (full swing Pierce)

1, 2

1

2

3

4

Depending on the crystal; a damping series resistor might be necessary

XCLKS negated during reset

f

osc

= 4 MHz, C = 22 pF.

Maximum value is for extreme cases using high Q, low frequency crystals

f

OSC

0.5

—

40

MHz

H2

P Startup Current

I

OSC

100

—

—

μ

A

H3

C Oscillator start-up time (loop controlled Pierce)

t

UPOSC

—

TBD

3

50

4

ms

H4

D Clock Quality check time-out

t

CQOUT

0.45

—

2.5

s

H5

P Clock Monitor Failure Assert Frequency

f

CMFA

50

100

200

KHz

H6

P External square wave input frequency

2

f

EXT

0.5

—

40

MHz

H7

D External square wave pulse width low

t

EXTL

9.5

—

—

ns

H8

D External square wave pulse width high

t

EXTH

9.5

—

—

ns

H9

D External square wave rise time

t

EXTR

—

—

1

ns

H10

D External square wave fall time

t

EXTF

—

—

1

ns

H11

D Input Capacitance (EXTAL, XTAL pins)

C

IN

—

7

—

pF

H12

C EXTAL pin DC Operating Bias in loop controlled

mode

V

DCBIAS

—

TBD

—

V

F

Freescale Semiconductor, Inc.

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAC7100MVF | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7100VFU | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7100VPV | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7100VVF | MAC7100 Microcontroller Family Hardware Specifications |

| MAC7101MVF | MAC7100 Microcontroller Family Hardware Specifications |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAC7100_04 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Reference Manual |

| MAC7100_0410 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontroller Family Reference Manual |

| MAC7100CFU | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MAC7100 Microcontroller Family Hardware Specifications |

| MAC7100CPV | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MAC7100 Microcontroller Family Hardware Specifications |

| MAC7100CVF | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:MAC7100 Microcontroller Family Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。