- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359095 > M74HC194M1R (意法半導體) 10-Bit, 3 or 9 us DAC, Serial Input, Pgrmable Settling Time/Pwr Consumption, Ultra Low Power 8-MSOP 0 to 70 PDF資料下載

參數(shù)資料

| 型號: | M74HC194M1R |

| 廠商: | 意法半導體 |

| 元件分類: | 通用總線功能 |

| 英文描述: | 10-Bit, 3 or 9 us DAC, Serial Input, Pgrmable Settling Time/Pwr Consumption, Ultra Low Power 8-MSOP 0 to 70 |

| 中文描述: | 4位皮普移位寄存器 |

| 文件頁數(shù): | 1/12頁 |

| 文件大小: | 271K |

| 代理商: | M74HC194M1R |

M54HC194

M74HC194

October 1992

4 BIT PIPO SHIFT REGISTER

B1R

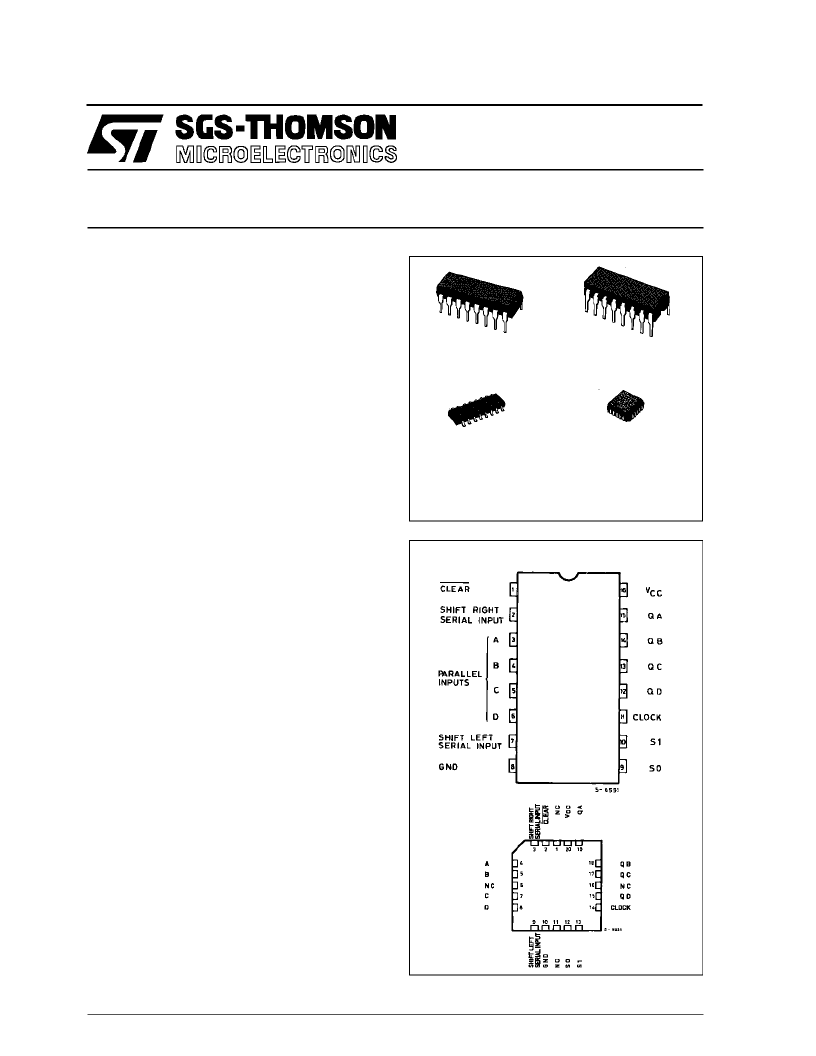

(Plastic Package)

ORDER CODES :

M54HC194F1R

M74HC194B1R

M74HC194M1R

M74HC194C1R

F1R

(CeramicPackage)

M1R

(MicroPackage)

C1R

(Chip Carrier)

PIN CONNECTIONS

(top view)

NC =

DESCRIPTION

TheM54/74HC194 isahighspeed CMOS4BITPIPO

SHIFTREGISTER fabricated in silicon gate C

2

MOS

technology. It has the same high speed performance

ofLSTTL combined with true CMOS lowpower con-

sumption. This SHIFT REGISTER is designed to in-

corporate virtuallyallofthefeaturesasystemdesigner

maywantina shift register. Itfeatures parallel inputs,

parallel outputs, right shift and left shift serial inputs,

clearline.Theregisterhasfourdistinctmodesofoper-

ation:PARALLEL (broadside) LOAD;SHIFTRIGHT

(in the direction Q

A

Q

D

); SHIFT LEFT ; INHIBIT

CLOCK(donothing). Synchronous parallel loading is

accomplished byapplyingthefourdatabitsand taking

both mode control inputs, S0 and S1 high. The data

are loaded into their respective flip-flops and appear

at the outputs after the positive transition of the

CLOCK input. During loading, serial data flow is in-

hibited.Shiftright isaccomplished synchronously with

therisingedge ofthe clockpulse whenS0ishigh and

S1 is low. Serial data for this mode is entered at the

SHIFTRIGHT data input. When S0 is lowand S1 is

high,data shiftsleftsynchronously andnewdataisen-

tered at the SHIFT LEFT serialinput. Clocking of the

flipflopsisinhibited whenbothmodecontrolinputsare

low.Themodecontrol inputsshouldbe changedonly

whentheCLOCKinput ishigh.Allinputsareequipped

with protection circuits against static discharge and

transient excess voltage.

.

HIGH SPEED

t

PD

= 12 ns(TYP.) AT V

CC

= 5 V

.

LOWPOWER DISSIPATION

I

CC

= 4

μ

A(MAX.) AT T

A

= 25

°

C

.

OUTPUT DRIVE CAPABILITY

10 LSTTL LOADS

.

SYMMETRICAL OUTPUT IMPEDANCE

I

OH

= I

OL

= 4 mA(MIN.)

.

BALANCEDPROPAGATION DELAYS

t

PLH

= t

PHL

.

HIGH NOISE IMMUNITY

V

NIH

= V

NIL

= 28 % V

CC

(MIN.)

.

WIDE OPERATING VOLTAGE RANGE

V

CC

(OPR) = 2 V TO6 V

.

PIN ANDFUNCTION COMPATIBLE

WITH 54/74LS194

1/12

相關PDF資料 |

PDF描述 |

|---|---|

| M74HC195B1R | 8 BIT PIPO SHIFT REGISTER |

| M74HC195 | 8 BIT PIPO SHIFT REGISTER |

| M74HC195C1R | 8 BIT PIPO SHIFT REGISTER |

| M74HC195M1R | 8 BIT PIPO SHIFT REGISTER |

| M74HC20B1R | DUAL 4-INPUT NAND GATE |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M74HC195 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8 BIT PIPO SHIFT REGISTER |

| M74HC195B1R | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8 BIT PIPO SHIFT REGISTER |

| M74HC195C1R | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8 BIT PIPO SHIFT REGISTER |

| M74HC195M1R | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8 BIT PIPO SHIFT REGISTER |

| M74HC20 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:DUAL 4-INPUT NAND GATE |

發(fā)布緊急采購,3分鐘左右您將得到回復。