- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370993 > M68HC05 (Motorola, Inc.) M68HC05 MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號(hào): | M68HC05 |

| 廠商: | Motorola, Inc. |

| 英文描述: | M68HC05 MICROCONTROLLERS |

| 中文描述: | M68HC05系列微控制器 |

| 文件頁(yè)數(shù): | 170/222頁(yè) |

| 文件大小: | 2253K |

| 代理商: | M68HC05 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)當(dāng)前第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)

T

M

—

1

I

M

I

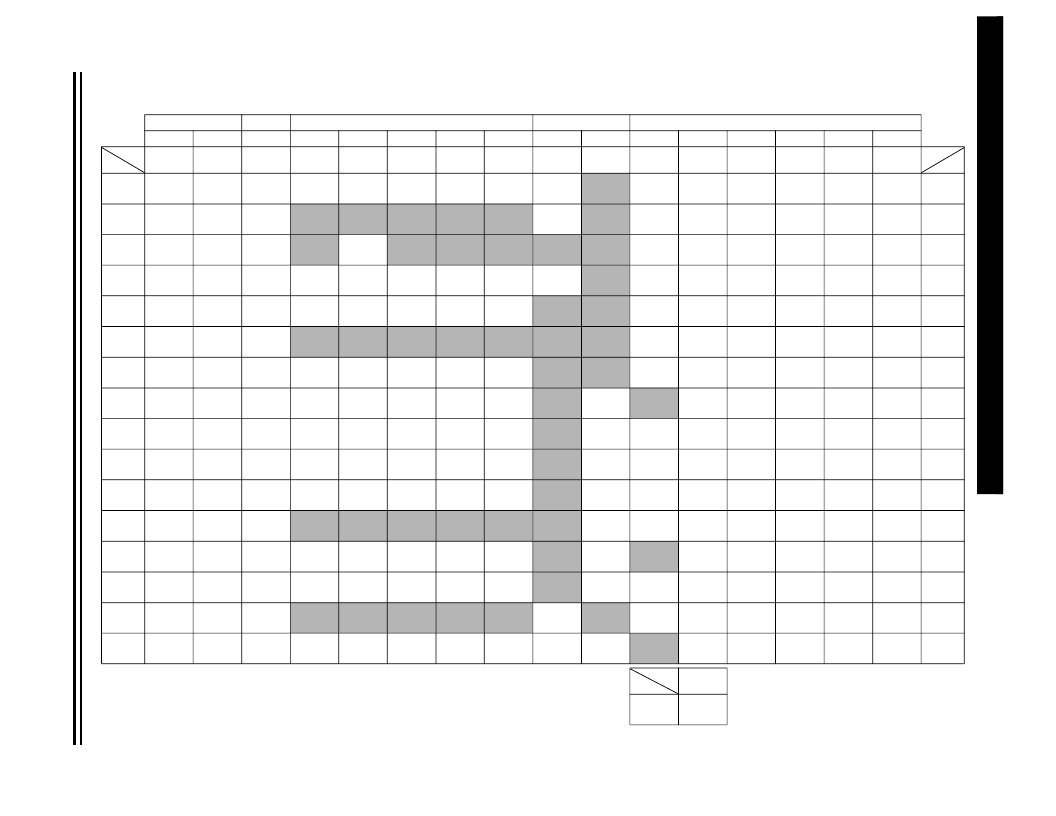

Table 12-7. Opcode Map

Bit Manipulation

DIR

Branch

REL

Read-Modify-Write

INH

INH

Control

INH

Register/Memory

EXT

DIR

DIR

IX1

IX

INH

IMM

DIR

IX2

IX1

IX

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

0

5

BRSET0

3

DIR

5

BSET0

2

DIR

3

BRA

2

REL

5

NEG

2

DIR

3

NEGA

1

INH

3

NEGX

1

INH

6

NEG

2

IX1

5

NEG

1

IX

9

RTI

1

INH

2

SUB

2

IMM

3

SUB

2

DIR

4

SUB

3

EXT

5

SUB

3

IX2

4

SUB

2

IX1

3

SUB

1

IX

3

0

1

5

BRCLR0

3

DIR

5

BCLR0

2

DIR

3

BRN

2

REL

6

RTS

1

INH

2

CMP

2

IMM

3

CMP

2

DIR

4

CMP

3

EXT

5

CMP

3

IX2

4

CMP

2

IX1

CMP

1

IX

3

1

2

5

BRSET1

3

DIR

5

BSET1

2

DIR

3

BHI

2

REL

11

MUL

1

INH

2

SBC

2

IMM

3

SBC

2

DIR

4

SBC

3

EXT

5

SBC

3

IX2

4

SBC

2

IX1

SBC

1

IX

3

2

3

5

BRCLR1

3

DIR

5

BCLR1

2

DIR

3

BLS

2

REL

5

COM

2

DIR

3

COMA

1

INH

3

COMX

1

INH

6

COM

2

IX1

5

COM

1

IX

5

10

SWI

1

INH

2

CPX

2

IMM

3

CPX

2

DIR

4

CPX

3

EXT

5

CPX

3

IX2

4

CPX

2

IX1

CPX

1

IX

3

3

4

5

BRSET2

3

DIR

5

BSET2

2

DIR

3

BCC

2

REL

5

LSR

2

DIR

3

LSRA

1

INH

3

LSRX

1

INH

6

LSR

2

IX1

LSR

1

IX

2

AND

2

IMM

3

AND

2

DIR

4

AND

3

EXT

5

AND

3

IX2

4

AND

2

IX1

AND

1

IX

3

4

5

5

BRCLR2

3

DIR

5

BCLR2

2

DIR

3

BCS/BLO

2

REL

2

BIT

2

IMM

3

BIT

2

DIR

4

BIT

3

EXT

5

BIT

3

IX2

4

BIT

2

IX1

BIT

1

IX

3

5

6

5

BRSET3

3

DIR

5

BSET3

2

DIR

3

BNE

2

REL

5

ROR

2

DIR

3

RORA

1

INH

3

RORX

1

INH

6

ROR

2

IX1

5

ROR

1

IX

5

2

LDA

2

IMM

3

LDA

2

DIR

4

LDA

3

EXT

5

LDA

3

IX2

4

LDA

2

IX1

LDA

1

IX

4

6

7

5

BRCLR3

3

DIR

5

BCLR3

2

DIR

3

BEQ

2

REL

5

ASR

2

DIR

3

ASRA

1

INH

3

ASRX

1

INH

6

ASR

2

IX1

ASR

1

IX

5

2

TAX

1

INH

4

STA

2

DIR

5

STA

3

EXT

6

STA

3

IX2

5

STA

2

IX1

STA

1

IX

3

7

8

5

BRSET4

3

DIR

5

BSET4

2

DIR

3

BHCC

2

REL

5

ASL/LSL

2

DIR

3

ASLA/LSLA

1

INH

3

ASLX/LSLX

1

INH

6

ASL/LSL

2

IX1

ASL/LSL

1

IX

5

2

CLC

1

INH

2

EOR

2

IMM

3

EOR

2

DIR

4

EOR

3

EXT

5

EOR

3

IX2

4

EOR

2

IX1

EOR

1

IX

3

8

9

5

BRCLR4

3

DIR

5

BCLR4

2

DIR

3

BHCS

2

REL

5

ROL

2

DIR

3

ROLA

1

INH

3

ROLX

1

INH

6

ROL

2

IX1

ROL

1

IX

5

2

SEC

1

INH

2

ADC

2

IMM

3

ADC

2

DIR

4

ADC

3

EXT

5

ADC

3

IX2

4

ADC

2

IX1

ADC

1

IX

3

9

A

5

BRSET5

3

DIR

5

BSET5

2

DIR

3

BPL

2

REL

5

DEC

2

DIR

3

DECA

1

INH

3

DECX

1

INH

6

DEC

2

IX1

DEC

1

IX

2

CLI

1

INH

2

ORA

2

IMM

3

ORA

2

DIR

4

ORA

3

EXT

5

ORA

3

IX2

4

ORA

2

IX1

ORA

1

IX

3

A

B

5

BRCLR5

3

DIR

5

BCLR5

2

DIR

3

BMI

2

REL

2

SEI

1

INH

2

ADD

2

IMM

3

ADD

2

DIR

4

ADD

3

EXT

5

ADD

3

IX2

4

ADD

2

IX1

ADD

1

IX

2

B

C

5

BRSET6

3

DIR

5

BSET6

2

DIR

3

BMC

2

REL

5

INC

2

DIR

3

INCA

1

INH

3

INCX

1

INH

6

INC

2

IX1

5

INC

1

IX

4

2

RSP

1

INH

2

JMP

2

DIR

3

JMP

3

EXT

4

JMP

3

IX2

3

JMP

2

IX1

JMP

1

IX

5

C

D

5

BRCLR6

3

DIR

5

BCLR6

2

DIR

3

BMS

2

REL

4

TST

2

DIR

3

TSTA

1

INH

3

TSTX

1

INH

5

TST

2

IX1

TST

1

IX

2

NOP

1

INH

6

BSR

2

REL

5

JSR

2

DIR

6

JSR

3

EXT

7

JSR

3

IX2

6

JSR

2

IX1

JSR

1

IX

3

D

E

5

BRSET7

3

DIR

5

BSET7

2

DIR

3

BIL

2

REL

2

STOP

1

INH

2

LDX

2

IMM

3

LDX

2

DIR

4

LDX

3

EXT

5

LDX

3

IX2

4

LDX

2

IX1

LDX

1

IX

4

E

F

5

BRCLR7

3

DIR

5

BCLR7

2

DIR

3

BIH

2

REL

5

CLR

2

DIR

3

CLRA

1

INH

3

CLRX

1

INH

6

CLR

2

IX1

5

CLR

1

IX

2

WAIT

1

INH

2

TXA

1

INH

4

STX

2

DIR

5

STX

3

EXT

6

STX

3

IX2

5

STX

2

IX1

STX

1

IX

F

INH = Inherent

IMM = Immediate

DIR = Direct

EXT = Extended

REL = Relative

IX = Indexed, No Offset

IX1 = Indexed, 8-Bit Offset

IX2 = Indexed, 16-Bit Offset

0

MSB of Opcode in Hexadecimal

LSB of Opcode in Hexadecimal

0

5

BRSET0

3

DIR

Number of Cycles

Opcode Mnemonic

Number of Bytes/Addressing Mode

LSB

MSB

LSB

MSB

LSB

MSB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M68HC11CPU | Single-Chip Microcontrollers (AMCU) |

| M68HC11 | Technical Data |

| M6M80011 | 1024 BIT ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM |

| M6M80011AP | 1024 BIT ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM |

| M6M80011FP | 1024 BIT ELECTRICALLY ERASABLE AND PROGRAMMABLE ROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M68HC05_13 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:M68HC05 Microcontrollers |

| M68HC05EVS | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Motorola M68HC05 Family Evaluation System |

| M68HC05M68H | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Microcontroller Unit |

| M68HC08 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| M68HC08M6 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:HCMOS Microcontroller Unit |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。