- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370992 > M66252P (Mitsubishi Electric Corporation) 1152 x 8-BIT LINE MEMORY FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | M66252P |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 1152 x 8-BIT LINE MEMORY FIFO |

| 中文描述: | 1152 × 8位線記憶先進(jìn)先出 |

| 文件頁數(shù): | 1/11頁 |

| 文件大小: | 145K |

| 代理商: | M66252P |

1

M66252P/FP

1152 x 8-BIT LINE MEMORY (FIFO)

1152 x 8-BIT LINE MEMORY (FIFO)

MIMITSUBISHI

DIDIGITAL ASSP

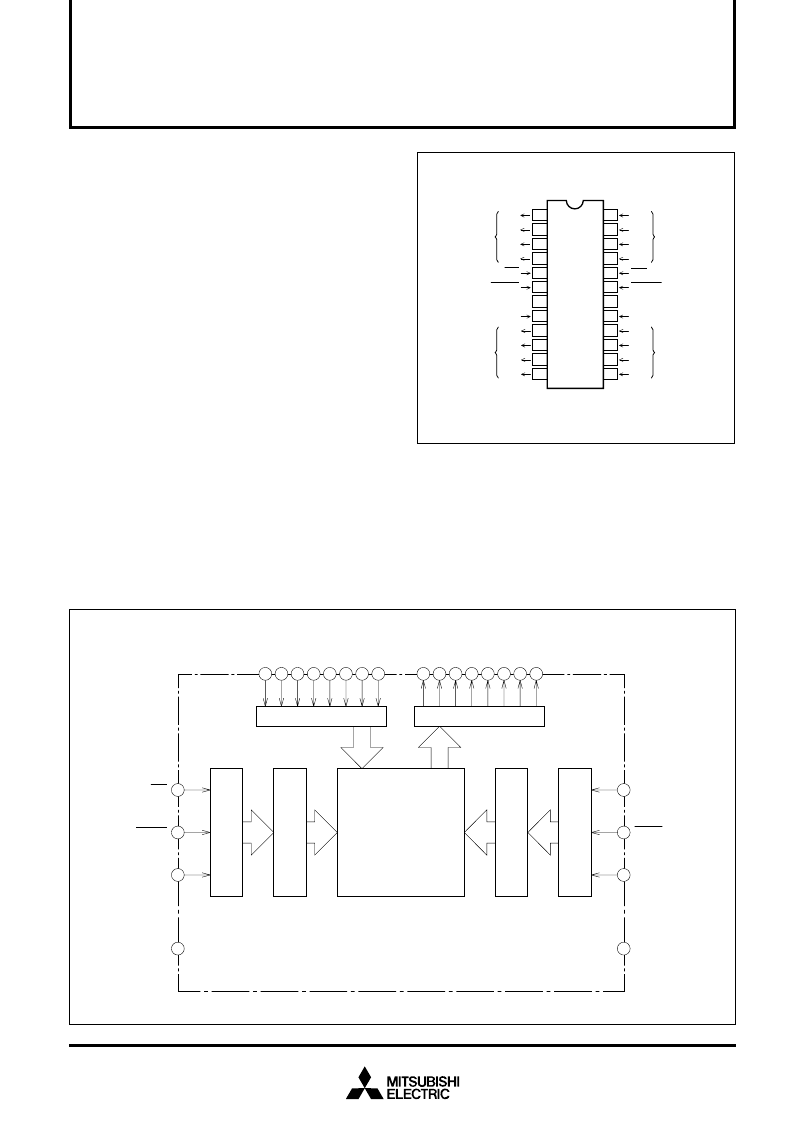

PIN CONFIGURATION (TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

14

13

15

16

19

18

17

20

21

22

23

24

M

Q

0

Q

1

Q

2

Q

3

RE

GND

RCK

Q

4

Q

5

Q

6

Q

7

D

0

D

1

D

2

D

3

WE

WRES

V

CC

WCK

D

4

D

5

D

6

D

7

Data output

Data output

Data input

Data input

24P4Y

24P2W-A

Outline

Read enable input

Read reset input

Read clock input

Write enable input

Write reset input

Write clock input

RRES

BLOCK DIAGRAM

24 23 22 21

16 15 14 13

Input buffer

1

2

3

4

9

10 11 12

Output buffer

20

19

17

18

W

W

Memory array

(1152 x 8 bits)

R

R

5

6

8

7

RE

RRES

RCK

GND

WE

WRES

WCK

Vcc

Write

enable input

Write

reset input

Write

clock input

Read

reset input

Read

enable input

Read

clock input

0

1

2

3

4

5

6

D

7

0

1

2

3

4

5

6

Q

7

Data input

Data output

DESCRIPTION

The M66252P/FP is a high-speed line memory with a FIFO

(First In First Out) structure of 1152-word

×

8-bit configuration

which uses high-performance silicon gate CMOS process

technology.

It has separate clock, enable and reset signals for write and

read and is most suitable as a buffer memory between

devices with different data processing throughput.

FEATURES

Memory construction ........................................................

............................. 1152words x 8bits (dynamic memory)

High-speed cycle ............................................ 50ns (min.)

High-speed access ........................................ 40ns (max.)

Output hold ....................................................... 5ns (min.)

Fully independent, asynchronous write and read opera-

tions

Variable-length delay bit

Output.................................................................... 3-state

APPLICATION

Digital photocopiers, high-speed facsimiles, laser beam print-

ers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66256 | 5120 x 8-BIT LINE MEMORY (FIFO) |

| M66256FP | 5120 x 8-BIT LINE MEMORY (FIFO) |

| M66257 | 5120 x 8-BIT x 2 LINE MEMORY (FIFO) |

| M66257FP | 5120 x 8-BIT x 2 LINE MEMORY (FIFO) |

| M66258 | 8192 x 8-BIT LINE MEMORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66255FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:8192 x 10-BIT LINE MEMORY (FIFO) |

| M66255FP(#TB0T) | 制造商:Renesas Electronics Corporation 功能描述: |

| M66256 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:5120 x 8-BIT LINE MEMORY (FIFO) |

| M66256FP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:5120 × 8-Bit Line Memory (FIFO) |

| M66256FP(#TF0T) | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。