- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370988 > M62500FP (Mitsubishi Electric Corporation) SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC PDF資料下載

參數(shù)資料

| 型號(hào): | M62500FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC |

| 中文描述: | 同步偏轉(zhuǎn)系統(tǒng)控制PWM集成電路 |

| 文件頁(yè)數(shù): | 7/11頁(yè) |

| 文件大?。?/td> | 110K |

| 代理商: | M62500FP |

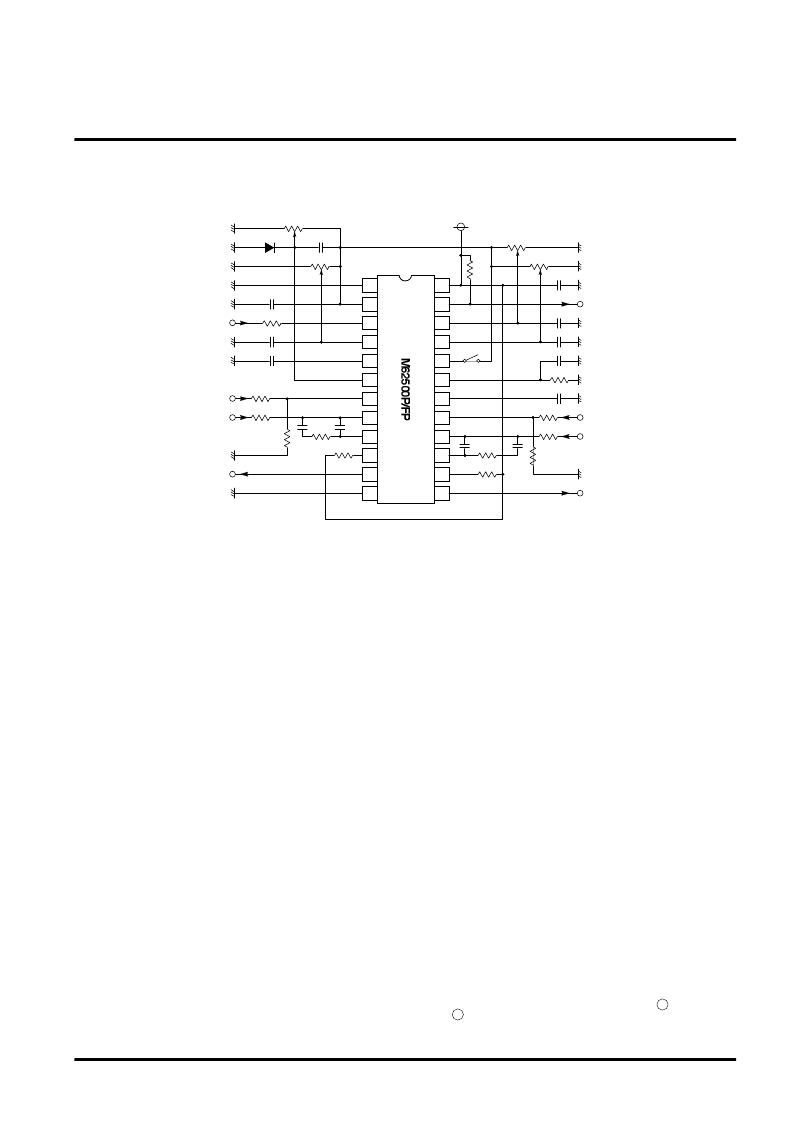

SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC

M62500P/FP

MITSUBISHI (Dig./Ana. INTERFACE)

( / 11 )

7

C1, C10

: Is required for stabilization of Vcc and V

REF

.

Is normally set to tens of μF to hundreds of

μF.

: Is determined taking into account the load

capability of V

REF

. (External load capability

of approx. 5mA) Shall be normally set to

approx. 10k

.

: Is added to high impedance pin of voltage

control for improvement in noise margin.

Depends on the device installation

environment. Shall be normally set to approx.

0.1μF.

: Is added for the execution of software start.

Set a time constant, taking into account the

set value of VR2.

: Is added to reduce interference by Tin and

outputs. With VIN=approx. 2.5V to 5V, the

resistance value of approx. 22k

is

recommended.

: Capacitance necessary for stabilization of

AGC. As the capacitance is larger, the

stability is larger, but the characteristic of

answering becomes worse. The capacitance

value of 1μF is recommended.

VR 1, 2, 3, 4

C2, C8, C9

C4, D1

R1

Cagc 1, 2

R2, R3, R10, R11 : A gain setup constant of error Amp. To

R4, R5, R8, R9

assure the stability of feedback, R4 and R8

C3, C4, C5, C6

shall be set to several k

to tens of k

to set

the gain to approx. 20dB to 40dB with f=1

kHz. If the gain is too low, jitter may take

place. It is therefore recommended to set C3

and C5 to tens of pF to hundreds of pF, C4

and C6 to thousands of pF to tens of

thousands of pF, and R5 and R9 to tens of

k

to hundreds of k

.

Ragc

: Resistance for setting AGC on the OUT2

side. Is set with Ragc=27k

.

C7

: If f to be input into Tin suddenly changes,

addition of C7 shortens non-control time of

Dout (output of "H"). As a capacitance value,

it is recommended to adopt 2.2μF. In the

case of adding C7, however,

Cagc2

≥

0.68μF is recommended.

R6, R7

: Current limit resistance of OUT1/2. Is

normally set to several

. Insertion of direct

limit resistance into OUT1/2 pin is also

effective.

R12

: Pull-up resistance of DOUT output. DOUT is

an open collector output and requires R12. Is

normally set to several k

.

* Note: To reduce interference in the signal system, pins GND and

P.GND shall be grounded at a point in the power supply block.

12

APPLICATION EXAMPLE

24

21

22

23

1

4

3

2

20

5

19

6

18

7

17

8

16

9

15

10

14

11

13

12

VR2

D1

C4

C1

R1

C2

Cagc1

Tin

VR1

R2

+IN1

R4

-IN1

R5

C4

C3

OUT1

R6

C10

VR4

VR3

C9

C8

DOUT

C7

Ragc

Cagc2

+IN2

R10

-IN2

R9

V

CC

OUT2

C6

C5

R7

R11

R3

R8

R12

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M62500P | SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC |

| M62501FP | PWM IC for the synchronized deflection system control |

| M62501P | PWM IC for the synchronized deflection system control |

| M62502FP | PWM IC for the synchronized deflection system control |

| M62551 | GENERAL PURPOSE C-MOS OP AMP(SINGLE/DUAL/QUAD) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M62500P | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SYNCHRONIZATION DEFLECTION SYSTEM CONTROL PWM IC |

| M62501FP | 制造商:Panasonic Industrial Company 功能描述:IC |

| M62501P | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:PWM IC for the Synchronized Deflection System Control |

| M62501P(#TF0J) | 制造商:Renesas Electronics Corporation 功能描述: |

| M62502FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PWM IC for the synchronized deflection system control |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。