- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370976 > M5M51016BTP-10VLL-I (Mitsubishi Electric Corporation) 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM PDF資料下載

參數(shù)資料

| 型號: | M5M51016BTP-10VLL-I |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| 中文描述: | 1048576位(65536字由16位)的CMOS靜態(tài)RAM |

| 文件頁數(shù): | 2/7頁 |

| 文件大小: | 76K |

| 代理商: | M5M51016BTP-10VLL-I |

MITSUBISHI LSIs

1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM

MITSUBISHI

ELECTRIC

M5M51016BTP,RT-10VL-I,

-10VLL-I

CS BC

1

BC

2

W

L

X

X

H

H

H

H

H

H

H

H

L

H

L

H

L

H

L

H

L

H

L

OE

X

X

X

L

H

X

L

H

X

L

H

Mode

Non selection

Non selection

DQ

1

~

8

DQ

9

~

16

High-Z

High-Z

High-Z

High-Z

High-Z

Din

Dout

High-Z

Din

Dout

High-Z

(High-Z=High-impedance)

Stand-by

Stand-by

Active

Active

Active

Active

Active

Active

Active

Active

Active

I

CC

X

H

L

L

L

H

H

H

L

L

L

X

X

L

H

H

L

H

H

L

H

H

High-Z

High-Z

Din

Dout

High-Z

High-Z

High-Z

High-Z

Din

Dout

High-Z

Upper-Byte Write

Upper-Byte Read

Lower-Byte Write

Lower-Byte Read

Word Write

Word Read

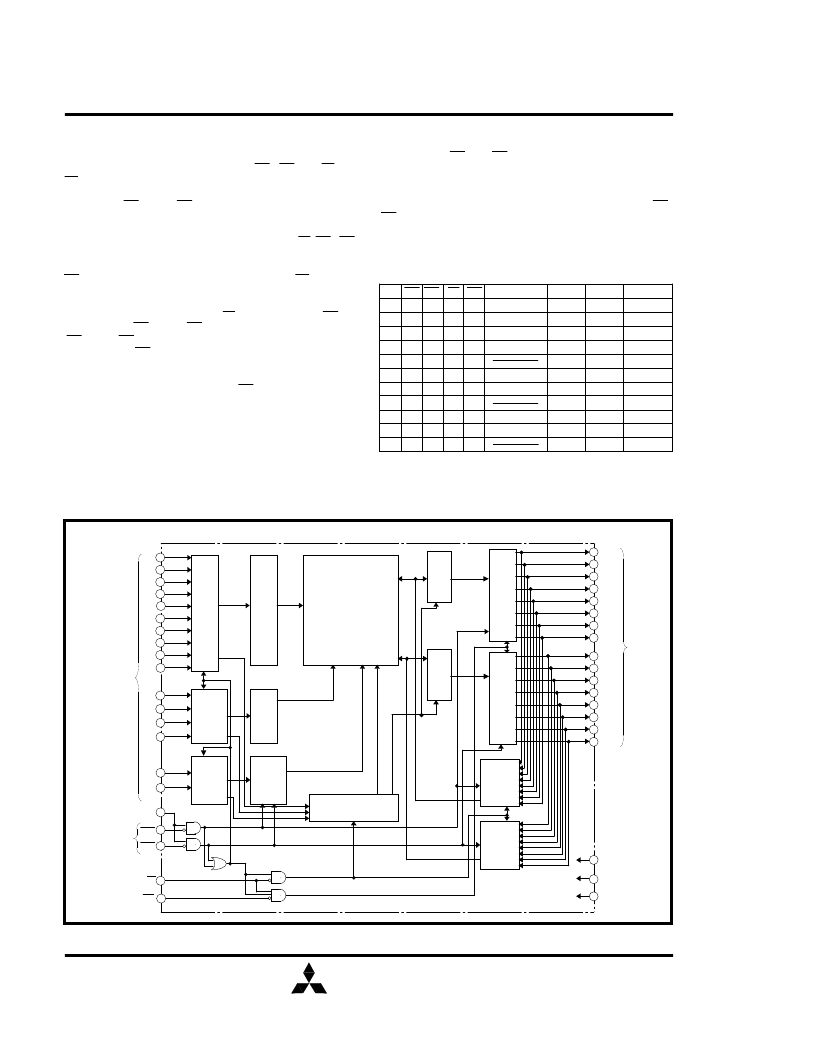

The operation mode of the M5M51016B series are determined by

a combination of the device control inputs BC

1

, BC

2

, CS, W and

OE. Each mode is summarized in the function table.

A write cycle is executed whenever the low level W overlaps with

the low level BC

1

and/or BC

2

and the high level CS. The address

must be set up before the write cycle and must be stable during

the entire cycle.

The data is latched into a cell on the trailing edge of W, BC

1

, BC

2

or CS, whichever occurs first, requiring the set-up and hold time

relative to these edge to be maintained. The output enable input

OE directly controls the output stage. Setting the OE at a high

level, the output stage is in a high-impedance state, and the

databus contention problem in the write cycle is eliminated.

A read cycle is executed by setting W at a high level and OE at a

low level while BC

1

and/or BC

2

and CS are in an active state.

(BC

1

and/or BC

2

=L,CS=H)

When setting BC

1

at a high level and the other pins are in an

active state, upper-Byte are in a selectable mode in which both

reading and writing are enabled, and lower-Byte are in a

non-selectable mode.And when setting BC

2

at a high level and the

other pins are in an active state, lower-Byte are in a selectable

mode and upper -Byte are in a non-selectable mode.

When setting BC

1

and BC

2

at a high level or CS at a low level,

the chips are in a non-selectable mode in which both reading and

writing are disabled.

In this mode, the output stage is in a high-impedance state,

allowing OR-tie with other chips and memory expansion by BC

1

,

BC

2

and CS. The power supply current is reduced as low as the

stand-by current which is specified as I

CC3

or I

CC4

, and the memory

data can be held at +2V power supply, enabling battery back-up

operation during powerfailure or power-down operation in the

non-selected mode.

A

1

9

A37

A64

A73

A12

A1441

A1540

A13 39

A837

A9 36

A

R

A0 10

A4 6

A2 8

A5 5

A10 34

A11 35

A

C

D

D

11

43

42

38

13

CS

BC1

BC2

W

OE

15DQ1

16DQ2

17DQ3

18 DQ4

19DQ5

20 DQ6

21 DQ7

22 DQ8

24DQ9

25DQ10

26DQ11

27DQ12

28DQ13

29DQ14

30DQ15

31DQ16

O

O

C

C

S

S

CLOCK

65536 WORDS x16 BITS

( 1024 ROWS

ADDRESS

INPUTS

CHIP SELECT

INPUT

CINPUTS

WRITE COINPUT

OUTPUT EINPUT

DATA

23Vcc

33GND(0V)

12 GND(0V)

BLOCK DIAGRAM

2

FUNCTION

A

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M51016RT-10L-I | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016RT-10LL-I | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016RT-10VLL-I | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016RT-12VL | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016RT-12VLL | 1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M51016BTP-12VL | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016BTP-12VL-I | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016BTP-12VLL | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016BTP-12VLL-I | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

| M5M51016BTP-70L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:1048576-BIT(65536-WORD BY 16-BIT)CMOS STATIC RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。