- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄180222 > M5LV-320/192-12AI (LATTICE SEMICONDUCTOR CORP) Fifth Generation MACH Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | M5LV-320/192-12AI |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | PLD |

| 英文描述: | Fifth Generation MACH Architecture |

| 中文描述: | EE PLD, 12 ns, PBGA256 |

| 封裝: | BGA-256 |

| 文件頁數(shù): | 19/47頁 |

| 文件大小: | 1145K |

| 代理商: | M5LV-320/192-12AI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

26

MACH 5 Family

1. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modied where

these parameters may be affected.

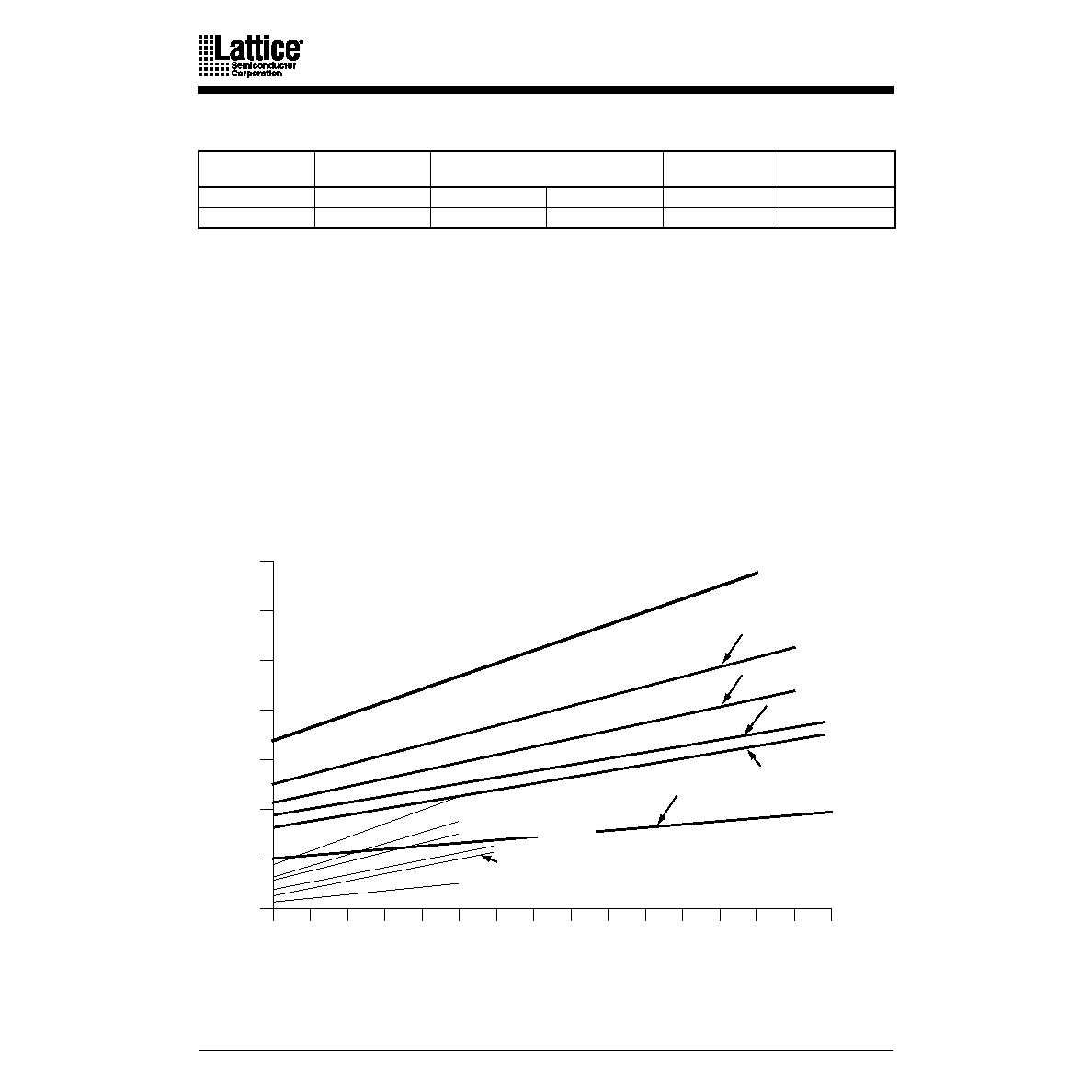

ICC vs. FREQUENCY

These curves represent the typical power consumption for a particular device at system frequency.

The selected “typical” pattern is a 16-bit up-down counter. This pattern lls the device and

exercises every macrocell. Maximum frequency shown uses internal feedback and a D-type

register. Power/Speed are optimized to obtain the highest counter frequency and the lowest

power. The highest frequency (LSBs) is placed in common PAL blocks, which are set to high

power. The lowest frequency signals (MSBs) are placed in a common PAL block and set to

lowest power. For a more detailed discussion about MACH 5 power consumption, refer to the

application note entitled MACH 5 Power in the Application Notes section on the Lattice Data Book

CD-ROM or Lattice web site.

ICC CURVES AT HIGH /LOW POWER MODES

CAPACITANCE1

Parameter Symbol

Parameter

Description

Test conditions

Typ

Unit

CIN

I/CLK pin

VIN =2.0 V

3.3 V or 5 V, 25 C, 1 MHz

12

pF

CI/O

I/O pin

VOUT =2.0 V

3.3 V or 5 V, 25 C, 1 MHz

10

pF

700

600

500

400

300

200

100

0

10

20

30

40

50

60

70

80

90

100

110

120

130

140

150

VCC = 5 V or 3.3 V, TA = 25 C

M5(LV)-512 high power

M5(LV)-384 high power

M5(LV)-320 high power

M5-256/1 and

M5LV-25 high power

M5-128/1 and M5LV-128 high power

M5(LV)-384 low power

M5(LV)-320 low power

M5-256/1 and M5LV-256 low power

M5-128/1 and M5LV-128 low power

I CC

(mA)

Frequency (MHz)

20446G-048

Figure 8. ICC Curves at High/Low Power Modes

M5-192/1 high power

M5-192/1 low power

M5(LV)-512 low power

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5LV-320/192-15AC | Fifth Generation MACH Architecture |

| M5LV-320/192-15AI | Fifth Generation MACH Architecture |

| M5LV-320/192-20AI | Fifth Generation MACH Architecture |

| M5LV-320/192-6AC | Fifth Generation MACH Architecture |

| M5LV-320/192-7AC | Fifth Generation MACH Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5LV-384/120-10YC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M5LV-384/120-10YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M5LV-384/120-12YC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M5LV-384/120-12YI | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| M5LV-384/120-15YC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 PROGRAM HI DENSITY CPLD RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。