- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377830 > M52S128168A (Elite Semiconductor Memory Technology Inc.) 1M x 16 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M52S128168A |

| 廠商: | Elite Semiconductor Memory Technology Inc. |

| 英文描述: | 1M x 16 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 100萬× 16位× 4個(gè)銀行同步DRAM |

| 文件頁數(shù): | 6/47頁 |

| 文件大小: | 1213K |

| 代理商: | M52S128168A |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

ES MT

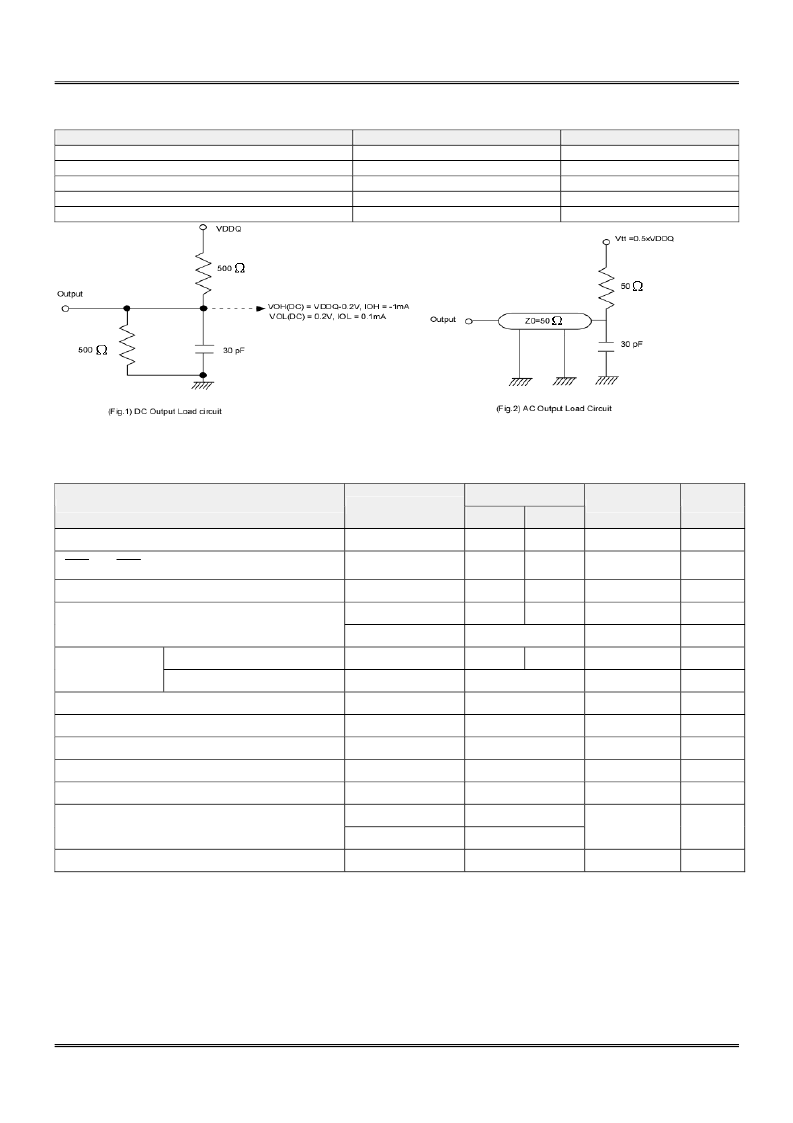

AC OPERATING TEST CONDITIONS

(V

DD

=2V

±

0.1V,T

A

= 0° ~ 70° )

Preliminary

M52S128168A

Elite Semiconductor Memory Technology Inc.

Revision

:

1.0

Publication Date

:

May. 2007

6/47

Parameter

Value

Unit

V

V

ns

V

Input levels (Vih/Vil)

Input timing measurement reference level

Input rise and fall time

Output timing measurement reference level

Output load condition

0.9 x V

DDQ

/ 0.2

0.5 x V

DDQ

tr / tf = 1 / 1

0.5 x V

DDQ

See Fig.2

OPERATING AC PARAMETER

(AC operating conditions unless otherwise noted)

Version

Parameter

Symbol

-7.5

-10

Unit

Note

Row active to row active delay

t

RRD

(min)

15

20

ns

1

RAS to CAS delay

t

RCD

(min)

15

20

ns

1

Row precharge time

t

RP

(min)

15

20

ns

1

t

RAS

(min)

48

50

ns

1

Row active time

t

RAS

(max)

100

us

-

@Operating

t

RC

(min)

63

90

ns

1

Row cycle time

@Auto refresh

t

RFC

(min)

80

ns

1 , 5

Last data in to new col. Address delay

t

CDL

(min)

1

CLK

2

Last data in to row precharge

t

RDL

(min)

2

CLK

2

Last data in to burst stop

t

BDL

(min)

1

CLK

2

Col. Address to col. Address delay

t

CCD

(min)

1

CLK

3

Mode Register command to Active or Refresh Command

t

MRD

(min)

2

CLK

-

CAS latency=3

2

Number of valid output data

CAS latency=2

1

ea

4

Refresh period(4,096 rows)

t

BEF

(max)

64

ms

6

Note:

1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and

then rounding off to the next higher integer.

3. Minimum delay is required to complete write.

4. All parts allow every cycle column address change.

5. In case of row precharge interrupt, auto precharge and read burst stop.

The earliest a precharge command can be issued after a Read command without the loss of data is CL+BL-2 clocks

5. A new command may be given t

RFC

after self refresh exit.

6. A maximum of eight consecutive AUTO REFRESH commands (with t

RFCmin

) can be posted to any given SDRAM,and

the maximum absolute interval between any AUTO REFRESH command and the next AUTO REFRESH command is

8x15.

6μs.)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M52S128168A-10BG | 1M x 16 Bit x 4 Banks Synchronous DRAM |

| M52S128168A-10TG | 1M x 16 Bit x 4 Banks Synchronous DRAM |

| M52S128168A-7.5BG | 1M x 16 Bit x 4 Banks Synchronous DRAM |

| M52S128168A-7.5TG | 1M x 16 Bit x 4 Banks Synchronous DRAM |

| M52S16161A | 512K x 16Bit x 2Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M52S128168A_08 | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:2M x 16 Bit x 4 Banks Synchronous DRAM |

| M52S128168A-10BG | 制造商:ELITE SEMICONDUCTOR 功能描述:SDRAM 128MB 2.5V 100MHZ FBGA54 |

| M52S128168A-10TG | 制造商:ELITE SEMICONDUCTOR 功能描述:SDRAM 128MB 2.5V 100MHZ TSOPII54 |

| M52S128168A-7.5BG | 制造商:ELITE SEMICONDUCTOR 功能描述:SDRAM 128MB 2.5V 133MHZ FBGA54 制造商:ELITE SEMICONDUCTOR 功能描述:SDRAM, 128MB, 2.5V, 133MHZ, FBGA54 制造商:ELITE SEMICONDUCTOR 功能描述:DRAM IC; Page Size:128MB; Memory Case Style:FBGA; No. of Pins:54; IC Interface Type:Parallel; Operating Temperature Min:0C; Operating Temperature Max:70C; Filter Terminals:Surface Mount; Frequency:133MHz; Interface Type:Parallel ;RoHS Compliant: Yes |

| M52S128168A-7.5TG | 制造商:ELITE SEMICONDUCTOR 功能描述:SDRAM 128MB 2.5V 133MHZ TSOPII54 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。