- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359067 > M48Z08-100PC1 (意法半導(dǎo)體) 64 Kbit 8Kb x 8 ZEROPOWER SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M48Z08-100PC1 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| 中文描述: | 64千位的8kB × 8 ZEROPOWER的SRAM |

| 文件頁數(shù): | 9/18頁 |

| 文件大小: | 141K |

| 代理商: | M48Z08-100PC1 |

DATA RETENTION MODE

With valid V

CC

applied, the M48Z08/18 operates as

a conventional BYTEWIDE

static RAM. Should

the supply voltage decay, the RAM will automat-

ically power-fail deselect, write protecting itself

when V

CC

falls within the V

PFD

(max), V

PFD

(min)

window. All outputs become high impedance, and

all inputs are treated as "don’t care."

Note:

A power failure during a write cycle may

corrupt data at the currently addressed location,

but does not jeopardize the rest of the RAM’s

content. At voltages below V

PFD

(min), the user can

be assured the memory will be in a write protected

state, provided the V

CC

fall time is not less than t

F

.

The M48Z08/18 may respond to transient noise

spikes on V

CC

that reach into the deselect window

during the time the device is sampling V

CC

. There-

fore, decoupling of the power supply lines is rec-

ommended.

When V

CC

drops below V

SO

, the control circuit

switches power to the internal battery which pre-

serves data and powers the clock. The internal

button cell will maintain data in the M48Z08/18 for

an accumulated period of at least 11 years when

V

CC

is less than V

SO

. As system power returns and

V

CC

rises above V

SO

, the battery is disconnected,

and the power supply is switched to external V

CC

.

Write protection continues until V

CC

reaches V

PFD

(min) plus t

REC

(min). E should be kept high as V

CC

rises past V

PFD

(min) to prevent inadvertent write

cycles prior to system stabilization. Normal RAM

operation can resume t

REC

after V

CC

exceeds

V

PFD

(max).

For more information on Battery Storage Life refer

to the Application Note AN1012.

SYSTEM BATTERY LIFE

The useful life of the battery in the M48Z08/18 is

expected to ultimately come to an end for one of

two reasons: either because it has been dis-

charged while providing current to the RAM in the

battery back-up mode, or because the effects of

aging render the cell useless before it can actually

be completely discharged. The two effects are

virtually unrelated, allowing discharge or Capacity

Consumption, and the effects of aging or Storage

Life, to be treated as two independent but simulta-

neous mechanisms. The earlier occurring failure

mechanism defines the battery system life of the

M48Z08/18.

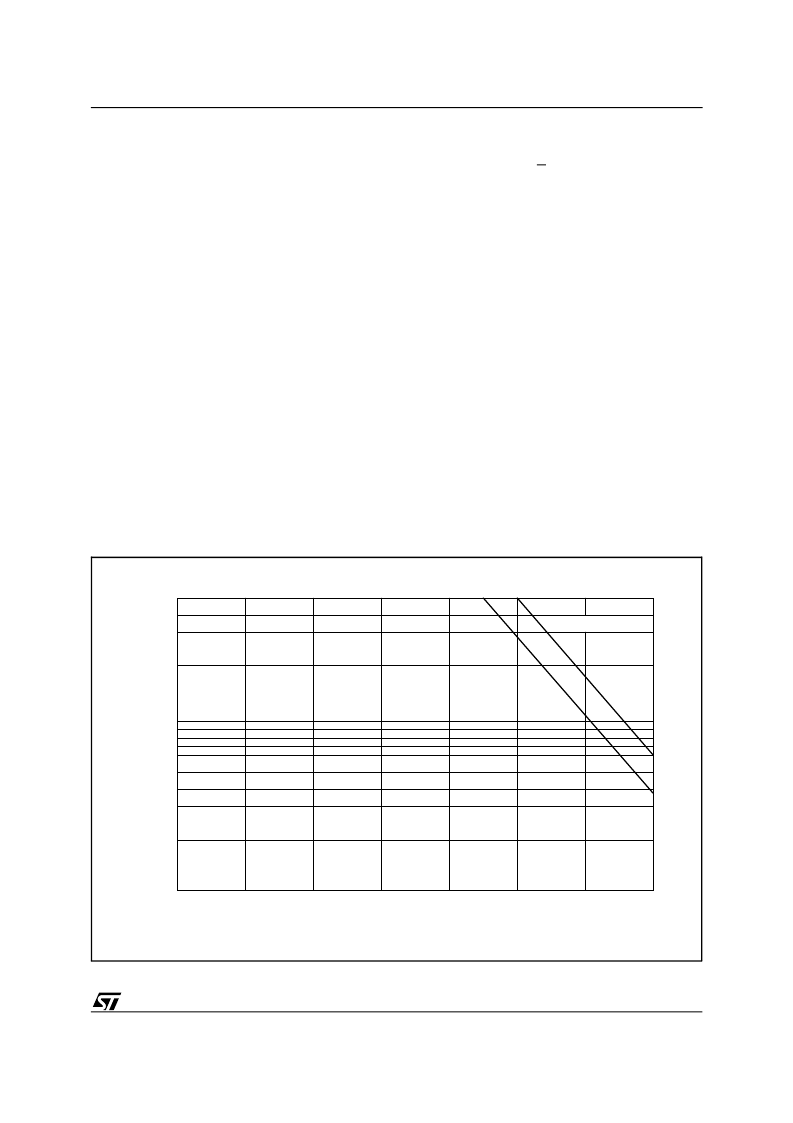

AI01399

20

30

40

50

60

70

80

90

1

2

3

4

5

8

6

TEMPERATURE (Degrees Celsius)

10

20

30

40

50

Y

t50% (AVERAGE)

t1%

Figure 9. Predicted Battery Storage Life versus Temperature

9/18

M48Z08, M48Z18

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48Z08-100MH6TR | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z08-100MH6 | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z08-100MH1TR | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z08PC | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

| M48Z08MH | 64 Kbit 8Kb x 8 ZEROPOWER SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48Z08-100PC1 | 制造商:STMicroelectronics 功能描述:ZEROPOWER SRAM 64K 48Z08 DIP28 |

| M48Z08-100PC1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V, 64 Kbit (8Kb x 8) ZEROPOWER㈢ SRAM |

| M48Z08-100PC6 | 制造商:STMicroelectronics 功能描述: |

| M48Z08-100PC6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:CMOS 8K x 8 TIMEKEEPER SRAM |

| M48Z08-150PC1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:16 Kbit 2Kb x 8 ZEROPOWER SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。