- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370923 > M38275M2-XXXFP (Mitsubishi Electric Corporation) Quad Low-Power Rail-to-Rail Input/Output Op Amp 14-SOIC 0 to 70 PDF資料下載

參數(shù)資料

| 型號: | M38275M2-XXXFP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | Quad Low-Power Rail-to-Rail Input/Output Op Amp 14-SOIC 0 to 70 |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 29/70頁 |

| 文件大小: | 1112K |

| 代理商: | M38275M2-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

29

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

3827 Group

Serial I/O2

The serial I/O2 function can be used only for clock synchronous

serial I/O.

For clock synchronous serial I/O2 the transmitter and the receiver

must use the same clock. When the internal clock is used, transfer

is started by a write signal to the serial I/O2 register.

When an internal clock is selected as the synchronous clock of the

serial I/O2, either P6

2

or P6

3

can be selected as an output pin of

the synchronous clock. In this case, the pin that is not selected as

an output pin of the synchronous clock functions as a port.

[Serial I/O2 Control Register (SIO2CON)]

001D

16

The serial I/O2 control register contains 8 bits which control vari-

ous serial I/O2 functions.

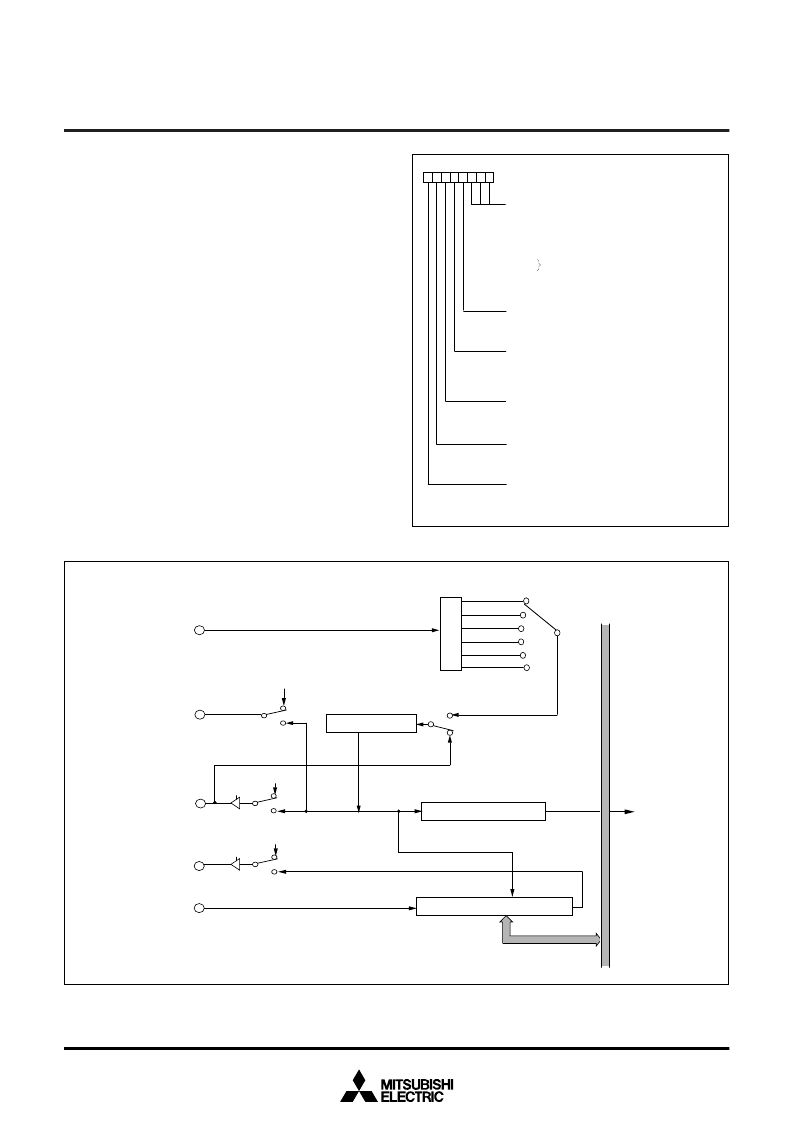

Fig. 26 Structure of serial I/O2 control register

Serial I/O2 control register

(SIO2CON : address 001D

16

)

Internal synchronous clock select bits

IN

)/8 (f(X

CIN

)/8 in low-speed mode)

0 0 1: f(X

IN

)/16 (f(X

CIN

)/16 in low-speed mode)

0 1 0: f(X

IN

)/32 (f(X

CIN

)/32 in low-speed mode)

0 1 1: f(X

IN

)/64 (f(X

CIN

)/64 in low-speed mode)

1 0 0:

1 0 1:

1 1 0: f(X

IN

)/128 (f(X

CIN

)/128 in low-speed mode)

1 1 1: f(X

IN

)/256 (f(X

CIN

)/256 in low-speed mode)

b7

Serial I/O2 port selection bit

0: I/O port

1: S

OUT2

,S

CLK21

/S

CLK22

signal output

P6

/S

P-channel output disable bit

0: CMOS output (in output mode)

1: N-channel open-drain output

(in output mode)

Transfer direction selection bit

0: LSB first

1: MSB first

Synchronous clock selection bit

0: External clock

1: Internal clock

Synchronous clock output pin selection bit

0: S

CLK21

1: S

CLK22

b0

b2 b1 b0

Do not set

Fig. 27 Block diagram of serial I/O2 function

f(X

IN

)

“1”

“0”

“0”

“1”

“0”

“1”

S

C

(Note)

1/8

1/16

1/32

1/64

1/128

1/256

Data bus

Serial I/O2

interrupt request

Serial I/O2 port selection bit

Serial I/O counter 2 (3)

Serial I/O shift register 2 (8)

Synchronous circuit

Synchronous clock

selection bit

External clock

Internal synchronous

clock select bits

D

P6

3

latch

P6

3

/S

CLK22

P6

2

/S

CLK21

P6

1

/S

OUT2

P6

0

/S

IN2

P6

2

latch

P6

1

latch

(Note)

Note:

It is selected by the synchronous clock selection bit, the synchronous

clock output pin selection bit, and the serial I/O port selection bit.

(f(X

CIN

) in low-speed mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38275M2-XXXFS | Quad Low-Power Rail-to-Rail Input/Output Op Amp 14-PDIP 0 to 70 |

| M38275M2-XXXGP | Quad Low-Power Rail-to-Rail Input/Output Op Amp 14-PDIP 0 to 70 |

| M38275M2-XXXHP | Quad Low-Power Rail-to-Rail Input/Output Op Amp 14-HTSSOP 0 to 70 |

| M38275MCMXXXFS | Quad Low-Power Rail-to-Rail Input/Output Op Amp w/Shutdown 16-SOIC -40 to 125 |

| M38275MCMXXXGP | Quad Low-Power Rail-to-Rail Input/Output Op Amp w/Shutdown 16-PDIP -40 to 125 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M3828 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 1000' |

| M3828 BK002 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 500' |

| M3828 BK005 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 100' |

| M3828 BK199 | 制造商:Alpha Wire Company 功能描述:CBL 3COND 16AWG BLK 3000=3000' |

| M3829 BK001 | 制造商:Alpha Wire Company 功能描述:CBL 4COND 16AWG BLK 1000' |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。