- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69015 > M38199MF-XXXFP 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | M38199MF-XXXFP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | 14 X 20 MM, 0.65 MM PITCH, PLASTIC, QFP-100 |

| 文件頁數(shù): | 27/63頁 |

| 文件大?。?/td> | 870K |

| 代理商: | M38199MF-XXXFP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

30

3819 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

A-D CONVERTER

The functional blocks of the A-D converter are described below.

A-D Conversion Register (AD) 002D16

The A-D conversion register is a read-only register that stores the

result of an A-D conversion. This register should not be read dur-

ing A-D conversion.

AD/DA Control Register (ADCON) 002C16

The AD/DA control register controls the A-D and the D-A conver-

sion process. Bits 0 to 3 of this register select analog input pins.

Bit 4 is the AD conversion completion bit. The value of this bit re-

mains at “0” during an A-D conversion, then changes to “1” when

the A-D conversion is completed.

The A-D conversion starts by writing “0” to this bit. Bit 6 controls

the output of D-A converter.

Comparison Voltage Generator

The comparison voltage generator divides the voltage between

AVSS and VREF by 256, and outputs the divided voltages.

Channel Selector

The channel selector selects one of the input ports P77/AN7–P70/

AN0, P57/SRDY3/AN15–P50/SIN2/AN8, and inputs to the compara-

tor.

Comparator and Control Circuit

The comparator and control circuit compares an analog input volt-

age with the comparison voltage and stores the result in the A-D

conversion register. When an A-D conversion is completed, the

control circuit sets the AD conversion completion bit and the AD

conversion interrupt request bit to “1”.

Note that the comparator is constructed linked to a capacitor, so

set f(XIN) to 500 kHz or more during A-D conversion.

Note : When using the A-D conversion interrupt, set the INT4/AD conver-

sion interrupt switch bit (the bit 5 of the interrupt selection register)

to “1”.

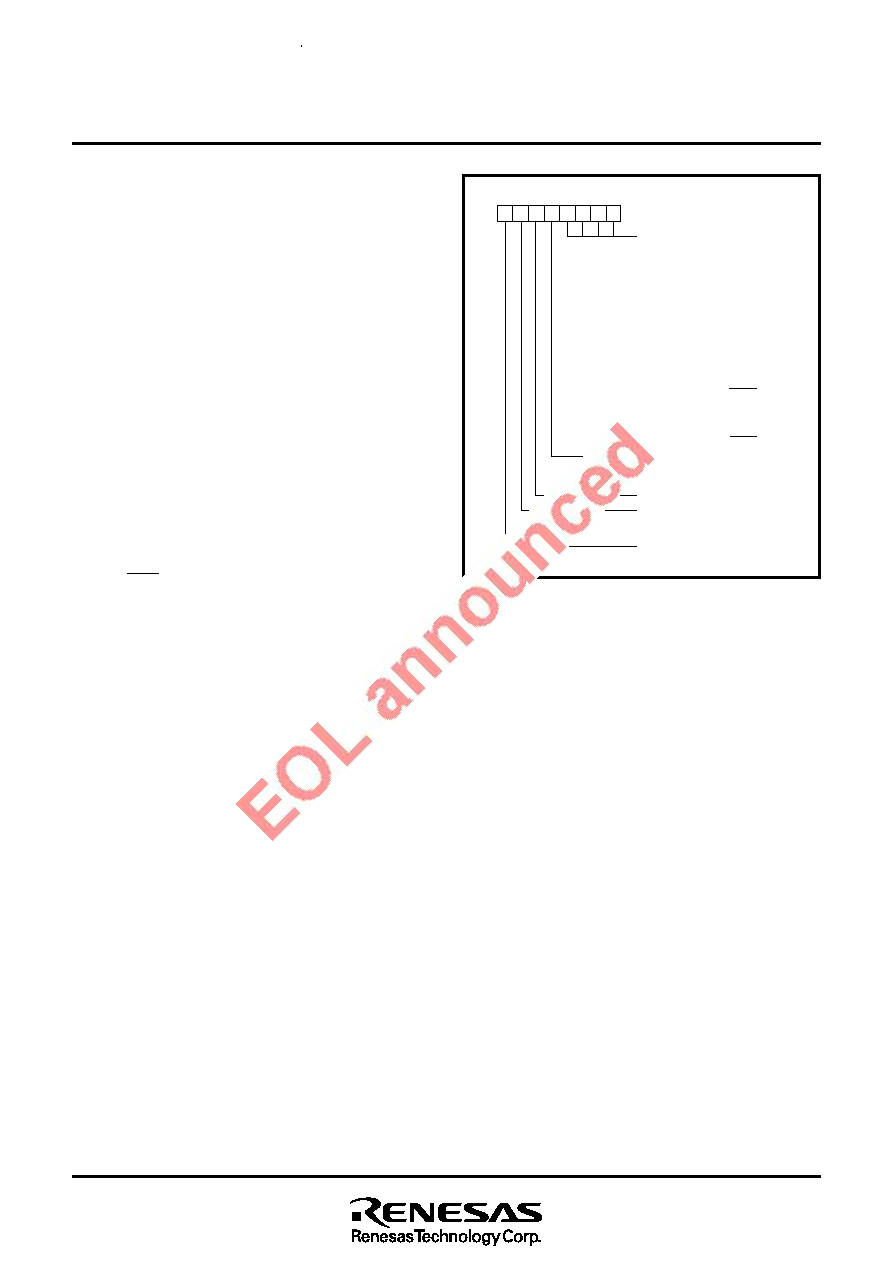

Fig. JA-1 Structure of A-D control register

Analog input pin selection bits

b3 b2 b1 b0

0 0 0 0 : P70/AN0

0 0 0 1 : P71/AN1

0 0 1 0 : P72/AN2

0 0 1 1 : P73/AN3

0 1 0 0 : P74/AN4

0 1 0 1 : P75/AN5

0 1 1 0 : P76/AN6

0 1 1 1 : P77/AN7

1 0 0 0 : P50/SIN2/AN8

1 0 0 1 : P51/SOUT2/AN9

1 0 1 0 : P52/SCLK2/AN10

1 0 1 1 : P53/SRDY2/AN11

1 1 0 0 : P54/SIN3/AN12

1 1 0 1 : P55/SOUT3/AN13

1 1 1 0 : P56/SCLK3/AN14

1 1 1 1 : P57/SRDY3/AN15

AD conversion completion bit

0 : Conversion in progress

1 : Conversion completed

Not used (returns “0” when read)

DA output enable bit

0 : Disable

1 : Enable

Not used (returns “0” when read)

b7

AD/DA control register

(ADCON : address 002C16)

b0

相關PDF資料 |

PDF描述 |

|---|---|

| M38199EF-XXXFP | 8-BIT, OTPROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38198MC-XXXKP | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38197MA-XXXFP | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38197MA-XXXKP | 8-BIT, MROM, 4.2 MHz, MICROCONTROLLER, PQFP100 |

| M38227M8A-XXXFP | 8-BIT, MROM, 5 MHz, MICROCONTROLLER, PQFP80 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M381A1G43BB0-CQB | 制造商:Samsung SDI 功能描述: |

| M381A1G73BB0-CQB | 制造商:Samsung SDI 功能描述: |

| M381A5173BB0-CQB | 制造商:Samsung SDI 功能描述: |

| M381L2923CUM-CB300 | 制造商:Samsung Semiconductor 功能描述:512MSDDDR_MDDR SDRAM MODULX72TSOP2-400(LF) - Bulk |

| M381L6423ETM-CA200 | 制造商:Samsung Semiconductor 功能描述:256 DDR SDRAM MODUL X72 TSOP2-400 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。