- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370902 > M38198MC-066 (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M38198MC-066 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機 |

| 文件頁數(shù): | 16/60頁 |

| 文件大小: | 664K |

| 代理商: | M38198MC-066 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

16

3819 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

INTERRUPTS

Interrupts occur by 20 sources: 5 external, 14 internal, and 1 soft-

ware.

Interrupt Control

Each interrupt is controlled by an interrupt request bit, an interrupt

enable bit, and the interrupt disable flag except for the software in-

terrupt set by the BRK instruction. An interrupt occurs if the

corresponding interrupt request and enable bits are “1” and the in-

terrupt disable flag is “0”.

Interrupt enable bits can be set or cleared by software.

Interrupt request bits can be cleared by software, but cannot be

set by software.

The BRK instruction cannot be disabled with any flag or bit.

The I (interrupt disable) flag disables all interrupts except the BRK

instruction interrupt.

Interrupt Operation

When an interrupt is received, the contents of the program counter

and processor status register are automatically stored into the

stack. The interrupt disable flag is set to inhibit other interrupts

from interfering. The corresponding interrupt request bit is cleared

and the interrupt jump destination address is read from the vector

table into the program counter.

Notes on Use

When the active edge of an external interrupt (INT

0

to INT

4

) is

changed or when switching interrupt sources in the same vector

address, the corresponding interrupt request bit may also be set.

Therefore, please take following sequence;

(1) Disable the external interrupt which is selected.

(2) Change the active edge.

(3) Clear the interrupt request bit which is selected to “0”.

(4) Enable the external interrupt which is selected.

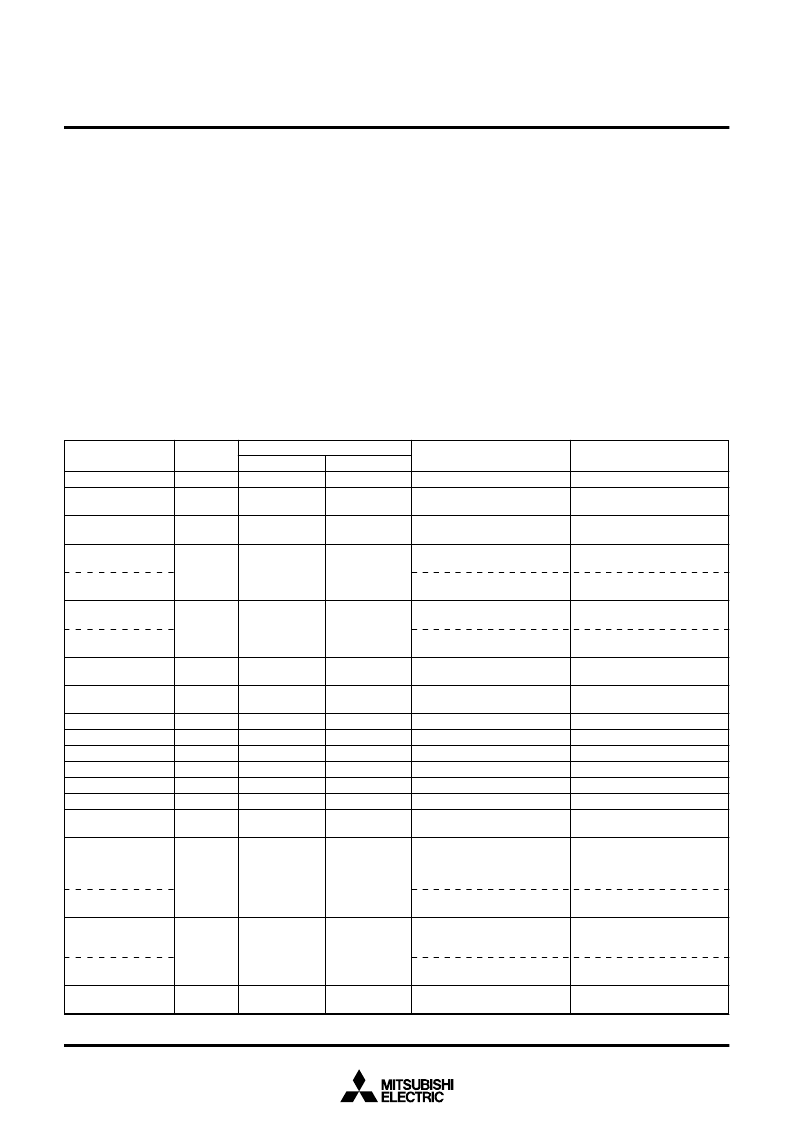

Table 1. Interrupt vector addresses and priority

Interrupt Request

Generating Conditions

High

FFFD

16

Interrupt Source

Priority

Low

FFFC

16

Remarks

Reset (Note 2)

Non-maskable

External interrupt (active edge

selectable)

External interrupt (active edge

selectable)

External interrupt (active edge

selectable)

Valid when interrupt interval

determination is operating

Valid when serial I/O ordinary

mode is selected

Valid when serial I/O automatic

transfer mode is selected

Valid when serial I/O2 is se-

lected

Valid when serial I/O3 is se-

lected

STP release timer underflow

1

Notes 1 :

Vector addresses contain interrupt jump destination addresses.

2 :

Reset function in the same way as an interrupt with the highest priority.

Vector Addresses (Note 1)

At reset

At detection of either rising or

falling edge of INT

0

input

At detection of either rising or

falling edge of INT

1

/ZCR input

At detection of either rising or

falling edge of INT

2

input

INT

0

INT

1

/ZCR

INT

2

Remote control/

counter overflow

Serial I/O1

Serial I/O

automatic transfer

Serial I/O2

Serial I/O3

Timer 1

Timer 2

Timer 3

Timer 4

Timer 5

Timer 6

INT

3

2

3

At 8-bit counter overflow

At completion of data transfer

At completion of the last data

transfer

At completion of data transfer

At completion of data transfer

At timer 1 underflow

At timer 2 underflow

At timer 3 underflow

At timer 4 underflow

At timer 5 underflow

At timer 6 underflow

At detection of either rising or

falling edge of INT

3

input

External interrupt (active edge

selectable)

Valid when INT

4

interrupt is

selected

External interrupt (active

edge selectable)

Valid when A-D conversion in-

terrupt is selected

At detection of either rising or

falling edge of INT

4

input

At completion of A-D conver-

sion

At falling edge of the last digit

immediately before blanking

period starts

At rising edge of each digit

At BRK instruction execution

Valid when FLD blanking in-

terrupt is selected

Valid when FLD digit interrupt

is selected

Non-maskable software inter-

rupt

FFFA

16

FFF8

16

FFF6

16

FFF4

16

FFF2

16

FFF0

16

FFEE

16

FFEC

16

FFEA

16

FFE8

16

FFE6

16

FFE4

16

FFE2

16

FFE0

16

FFDE

16

FFDC

16

FFFB

16

FFF9

16

FFF7

16

FFF5

16

FFF3

16

FFF1

16

FFEF

16

FFED

16

FFEB

16

FFE9

16

FFE7

16

FFE5

16

FFE3

16

FFE1

16

FFDF

16

FFDD

16

4

5

6

7

8

9

10

11

12

13

14

15

16

17

INT

4

A-D conversion

FLD blanking

FLD digit

BRK instruction

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38198MC-066FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38198MC-083FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38198MC-085FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38198MC-087FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38198MC-103FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38198MCA809 | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38198MCA824 | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38198MCA827 | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38199MF072F | 制造商:Panasonic Industrial Company 功能描述:IC |

| M38199MF210F | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。