- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370848 > M37735MHLXXXHP (Mitsubishi Electric Corporation) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M37735MHLXXXHP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機(jī) |

| 文件頁(yè)數(shù): | 7/34頁(yè) |

| 文件大小: | 591K |

| 代理商: | M37735MHLXXXHP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

7

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

MITSUBISHI MICROCOMPUTERS

M37735EHBXXXFP

M37735EHBFS

PROM VERSION OF M37735MHBXXXFP

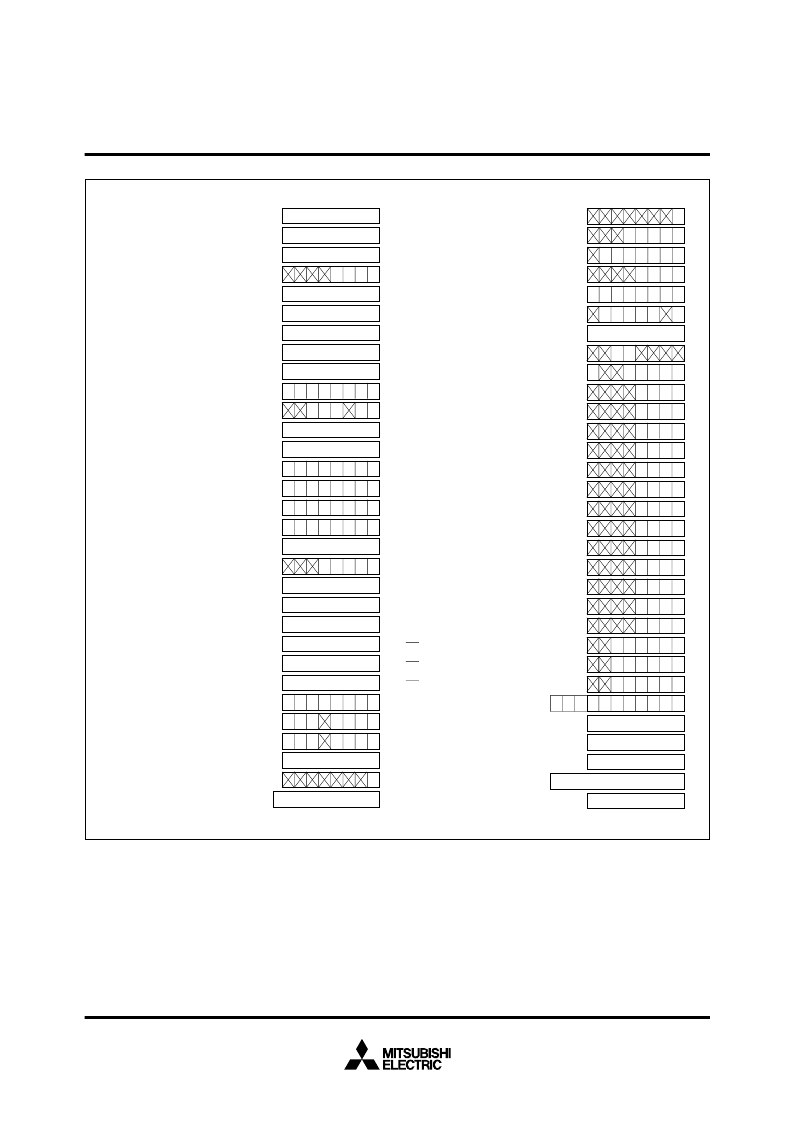

Fig. 3 Microcomputer internal status during reset

Address

00

16

0 0 0 0

00

16

00

16

00

16

00

16

00

16

00

16

0

1 1

0 0

0 0

0

0

00

16

00

16

0

0 0

0 0

0 0

0 0

0 0

0 0

0 0

0 0

1 0

0 0

0 0

1 0

0 0

0 0

1 0

1 0

00

16

0 0 0

0

0

00

16

00

16

00

16

00

16

00

16

00

16

0

0 0 1

0 0

0

0

0 0 1

0 0 1

0 0

0

0

0 0

0

0

0

00

16

(04

16

)

(05

16

)

(08

16

)

(09

16

)

(0C

16

)

(0D

16

)

(10

16

)

(11

16

)

(14

16

)

(1E

16

)

(1F

16

)

(30

16

)

(38

16

)

(34

16

)

(3C

16

)

(35

16

)

(3D

16

)

(40

16

)

(42

16

)

(44

16

)

(56

16

)

(57

16

)

(58

16

)

(59

16

)

(5A

16

)

(5B

16

)

(5C

16

)

(5D

16

)

(5E

16

)

(5F

16

)

Port P0 direction register

Port P1 direction register

Port P2 direction register

Port P3 direction register

Port P4 direction register

Port P5 direction register

Port P6 direction register

Port P7 direction register

Port P8 direction register

A-D control register 0

A-D control register 1

UART 0 transmit/receive mode register

UART 1 transmit/receive

control register 1

Count start flag

UART 1 transmit/receive mode register

UART 0 transmit/receive

control register 0

UART 1 transmit/receive

control register 0

UART 0 transmit/receive

control register 1

One- shot start flag

Up-down flag

Timer A0 mode register

Timer A1 mode register

Timer A2 mode register

Timer A3 mode register

Timer A4 mode register

Timer B0 mode register

Timer B1 mode register

Timer B2 mode register

Processor mode register 0

Processor mode register 1

Address

(60

16

)

(7F

16

)

(6C

16

)

(6D

16

)

(6E

16

)

(6F

16

)

(70

16

)

(71

16

)

(72

16

)

(73

16

)

(74

16

)

(75

16

)

(76

16

)

(77

16

)

(78

16

)

(79

16

)

(7A

16

)

(7B

16

)

(7C

16

)

(7D

16

)

(7E

16

)

Watchdog timer register

Oscillation circuit control register 0

Port function control register

Serial transmit control register

Oscillation circuit control register 1

A-D/UART2 trans./rece. interrupt control register

UART 0 transmission interrupt control register

UART 0 receive interrupt control register

UART 1 transmission interrupt control register

UART 1 receive interrupt control register

Timer A0 interrupt control register

Timer B2 interrupt control register

Timer A1 interrupt control register

Timer A2 interrupt control register

Timer A3 interrupt control register

Timer A4 interrupt control register

Timer B0 interrupt control register

Timer B1 interrupt control register

Processor status register (PS)

Program bank register (PG)

Program counter (PC

H

)

Program counter (PC

L

)

Direct page register (DPR)

Data bank register (DT)

INT

0

interrupt control register

0

0

0

Contents of other registers and RAM are undefined during reset. Initialize them by software.

0

0

0

0 0 0 0

0

0 0 1

0 0 0

0 0 0

0 0 0

0 0 0

1

0

1

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0

0

0

0

0 0

0 0

0

0

0

00

16

00

16

Content of FFFF

16

Content of FFFE

16

0000

16

FFF

16

0

0

0

0

0

0

INT

1

interrupt control register

INT

2

/Key input interrupt control register

00

16

(61

16

)

(63

16

)

(64

16

)

(68

16

)

Watchdog timer frequency selection flag

Memory allocation control register

UART2 transmit/receive mode register

UART2 transmit/receive control register 0

0 0

0

0 0 1

0

0 0

(69

16

)

UART2 transmit/receive control register 1

0

0 0 0

0

0 0

0 0 0

1

0

0 1 0

0

0 0

0

00

16

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37735MHBXXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37735MHL-143HP | PROM VERSION OF M37735MHLXXXHP |

| M37735M4B | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37735M4BXXXFP | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| M37735M4L | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37735S4BFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37735S4LHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37735T-PAC | 制造商:Renesas Electronics Corporation 功能描述:DEV 7733 SIMPLE DEVELOPMENT TOOL PACKAGE - Bulk |

| M37736EHB | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PROM VERSION OF M37736EHBXXXGP |

| M37736EHBGS | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:PROM VERSION OF M37736MHBXXXGP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。