- 您現(xiàn)在的位置:買賣IC網 > PDF目錄370848 > M37733S4 (Mitsubishi Electric Corporation) 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號: | M37733S4 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 16位CMOS微機 |

| 文件頁數(shù): | 16/35頁 |

| 文件大?。?/td> | 726K |

| 代理商: | M37733S4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

PRELIMINARY

Notice: This is not a final specification.

Some parametric limits are subject to change.

16

MITSUBISHI MICROCOMPUTERS

M37733EHLXXXHP

PROM VERSION OF M37733MHLXXXHP

V

CC

= 5 V,

f(X

IN

) = 12 MHz (square waveform),

(f(f

2

) = 6 MHz),

f(X

CIN

) = 32.768 kHz,

in operating (Note 1)

V

CC

= 3 V,

f(X

IN

) = 12 MHz (square waveform),

(f(f

2

) = 6 MHz),

f(X

CIN

) = 32.768 kHz,

in operating (Note 1)

V

CC

= 3 V,

f(X

IN

) = 12 MHz (square waveform),

(f(f

2

) = 0.75 MHz),

f(X

CIN

) : Stopped,

in operating

V

CC

= 3 V,

f(X

IN

) = 12 MHz (square waveform),

f(X

CIN

) = 32.768 kHz,

when a WIT instruction is executed (Note 2)

V

CC

= 3 V,

f(X

IN

) : Stopped,

f(X

CIN

) = 32.768 kHz,

in operating (Note 3)

V

CC

= 3 V,

f(X

IN

) : Stopped,

f(X

CIN

) = 32.768 kHz,

when a WIT instruction is executed (Note 4)

Ta = 25 °C,

when clock is stopped

Ta = 85 °C,

when clock is stopped

mA

mA

mA

μ

A

μ

A

μ

A

μ

A

μ

A

Max.

9

6

0.8

12

60

6

1

20

Limits

Typ.

4.5

3

0.4

6

30

3

Unit

Min.

Test conditions

Symbol

Parameter

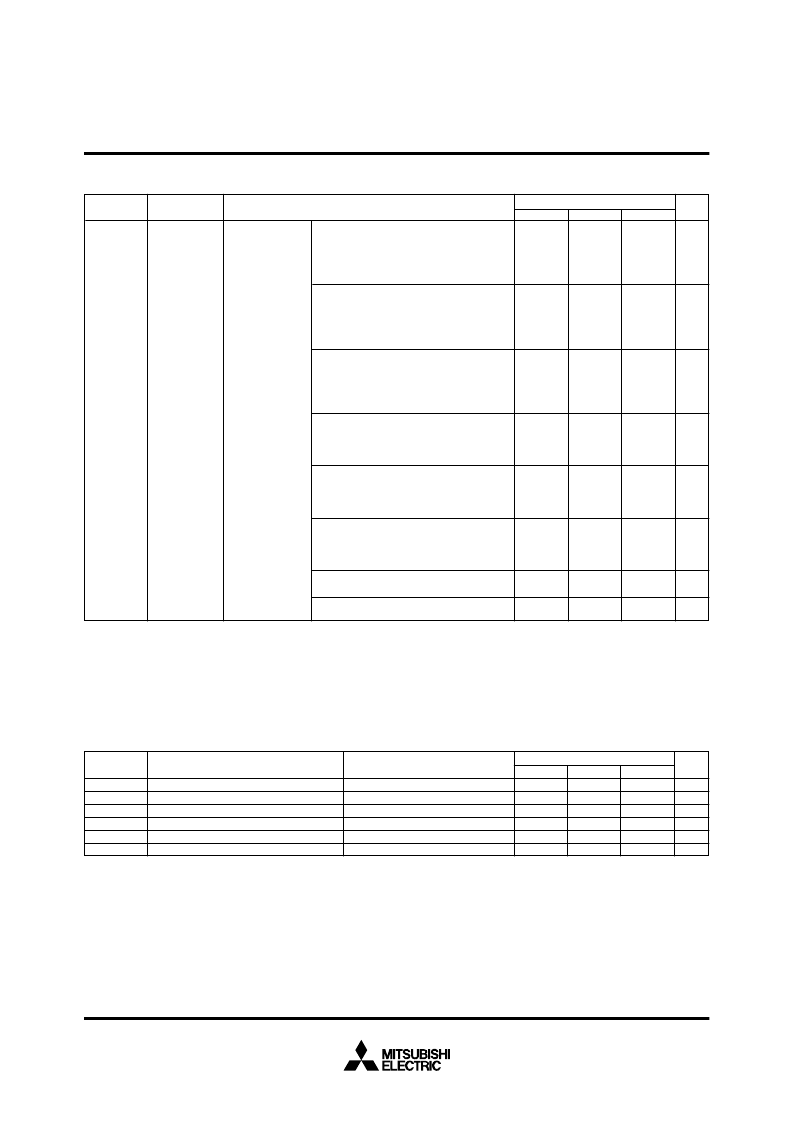

ELECTRICAL CHARACTERISTICS

(Vcc = 5 V, Vss = 0 V, Ta = –40 to +85 °C, unless otherwise noted)

When single-chip

mode, output pins

are open, and

other pins are V

SS

.

Power source

current

I

CC

Limits

Typ.

Min.

Max.

10

± 3

25

—

—

R

LADDER

t

CONV

V

REF

V

IA

Note.

This applies when the main clock division selection bit = “0” and f(f

2

) = 6 MHz.

Resolution

Absolute accuracy

Ladder resistance

Conversion time

Reference voltage

Analog input voltage

V

REF

= V

CC

V

REF

= V

CC

V

REF

= V

CC

Bits

LSB

k

s

V

V

10

19.6

2.7

V

CC

V

REF

0

Symbol

Parameter

Test conditions

Unit

A–D CONVERTER CHARACTERISTICS

(V

CC

= AV

CC

= 5 V, V

SS

= AV

SS

= 0 V, Ta = –40 to +85 °C, f(X

IN

) = 12 MHz, unless otherwise noted (Note))

Notes 1.

This applies when the main clock external input selection bit = “1”, the main clock division selection bit = “0”, and the signal output stop

bit = “1”.

2.

This applies when the main clock external input selection bit = “1” and the system clock stop bit at wait state = “1”.

3.

This applies when CPU and the clock timer are operating with the sub clock (32.768 kHz) selected as the system clock.

4.

This applies when the X

COUT

drivability selection bit = “0” and the system clock stop bit at wait state = “1”.

μ

相關PDF資料 |

PDF描述 |

|---|---|

| M37733S4BFP | 16-BIT CMOS MICROCOMPUTER |

| M37733EHL | Single Chip 16 Bits CMOS Microcomputer(16位單片機) |

| M37733MHB-217FP | PROM VERSION OF M37733MHBXXXFP(MICROCOMPUTERS) |

| M37733MHB274FP | PROM VERSION OF M37733MHBXXXFP(MICROCOMPUTERS) |

| M37733 | 16-BIT CMOS MICROCOMPUTER |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M37733S4BFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37733S4LHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT CMOS MICROCOMPUTER |

| M37733TL-HPD | 制造商:Renesas Electronics Corporation 功能描述:DEV 7733 GROUP EMULATION POD - Bulk |

| M37735EHB | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:PROM VERSION OF M37735EHBXXXFP |

| M37735EHBFS | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:PROM VERSION OF M37735MHBXXXFP |

發(fā)布緊急采購,3分鐘左右您將得到回復。