- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370845 > M37510M1156FP (Mitsubishi Electric Corporation) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M37510M1156FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片8位CMOS微機(jī) |

| 文件頁數(shù): | 40/43頁 |

| 文件大?。?/td> | 614K |

| 代理商: | M37510M1156FP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁

40

7510 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

SWITCHING CHARACTERISTICS 1

(V

CC

= 4.0 to 5.5 V, V

SS

= 0 V, T

a

= –20 to 85

°

C, unless otherwise noted)

Symbol

t

wH(S

CLK1

)

t

wH(S

CLK2

)

t

wL(S

CLK1

)

t

wL(S

CLK2

)

t

d(S

CLK1

–T

X

D

1

)

t

d(S

CLK2

–T

X

D

2

)

t

v(S

CLK1

–T

X

D

1

)

t

v(S

CLK2

–T

X

D

2

)

t

r(S

CLK1

)

t

f(S

CLK1

)

t

r(S

CLK2

)

t

f(S

CLK2

)

t

r

(CMOS)

t

f

(CMOS)

Parameter

Serial I/O1 clock output “H” pulse width

Serial I/O2 clock output “H” pulse width

Serial I/O1 clock output “L” pulse width

Serial I/O2 clock output “L” pulse width

Serial I/O1 output delay time (Note 1)

Serial I/O2 output delay time (Note 1)

Serial I/O1 output valid time (Note 1)

Serial I/O2 output valid time (Note 1)

Serial I/O1 clock output rise time

Serial I/O1 clock output fall time

Serial I/O2 clock output rise time

Serial I/O2 clock output fall time

CMOS output rise time (Note 2)

CMOS output fall time (Note 2)

Test conditions

C

L

= 100 pF

Limits

Min.

t

c(S

CLK1

)/2–30

t

c(S

CLK2

)/2–30

t

c(S

CLK1

)/2–30

t

c(S

CLK2

)/2–30

–30

–30

Typ.

10

10

Max.

140

140

30

30

30

30

30

30

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes 1:

When bit 4 of the UART control register (address 001B

16

or 0033

16

) is “0”.

2:

X

OUT

pin is excluded.

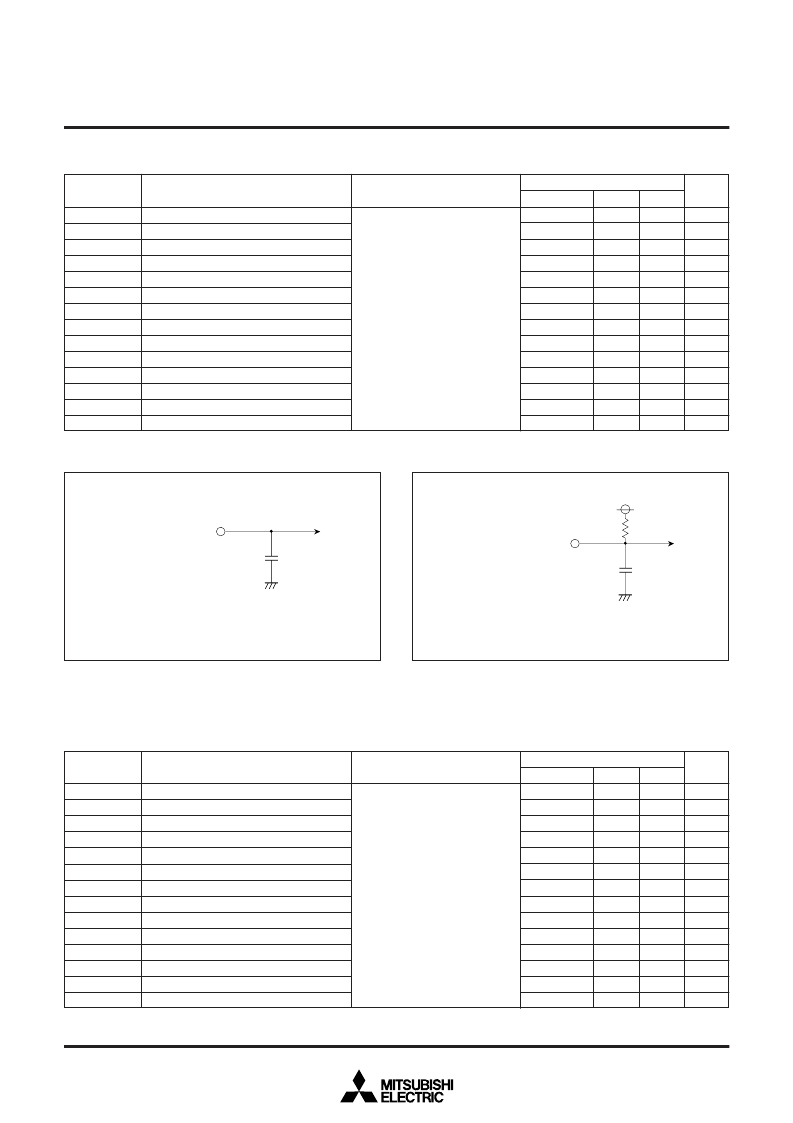

Fig. 34 Circuit for measuring output switching characteristics (1)

Fig. 35 Circuit for measuring output switching characteristics (2)

Note:

When bit 4 of the UART contronl register (address 001B

16

or 0033

16

)

is “1” (N-channel open-drain output), and bit 7 of the serial I/O con-

trol register (address 001A

16

or 0032

16

) is “1”.

SWITCHING CHARACTERISTICS 2

(V

CC

= 3.0 to 5.5 V, V

SS

= 0 V, T

a

= –20 to 85

°

C, unless otherwise noted)

Symbol

t

wH(S

CLK1

)

t

wH(S

CLK2

)

t

wL(S

CLK1

)

t

wL(S

CLK2

)

t

d(S

CLK1

–T

X

D

1

)

t

d(S

CLK2

–T

X

D

2

)

t

v(S

CLK1

–T

X

D

1

)

t

v(S

CLK2

–T

X

D

2

)

t

r(S

CLK1

)

t

f(S

CLK1

)

t

r(S

CLK2

)

t

f(S

CLK2

)

t

r

(CMOS)

t

f

(CMOS)

Parameter

Serial I/O1 clock output “H” pulse width

Serial I/O2 clock output “H” pulse width

Serial I/O1 clock output “L” pulse width

Serial I/O2 clock output “L” pulse width

Serial I/O1 output delay time (Note 1)

Serial I/O2 output delay time (Note 1)

Serial I/O1 output valid time (Note 1)

Serial I/O2 output valid time (Note 1)

Serial I/O1 clock output rise time

Serial I/O1 clock output fall time

Serial I/O2 clock output rise time

Serial I/O2 clock output fall time

CMOS output rise time (Note 2)

CMOS output fall time (Note 2)

Test conditions

C

L

= 100 pF

Limits

Min.

t

c(S

CLK1

)/2–50

t

c(S

CLK2

)/2–50

t

c(S

CLK1

)/2–50

t

c(S

CLK2

)/2–50

–30

–30

Typ.

20

20

Max.

350

350

50

50

50

50

50

50

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes 1:

When bit 4 of the UART control register (address 001B

16

or 0033

16

) is “0”.

2:

X

OUT

pin excluded.

100pF

CMOS output

Measurement output pin

100pF

N-channel open-drain output

Measurement output pin

1k

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37510M2156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M3156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M4156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M5156FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M6 | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37510M2156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M3156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M4156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M5156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M6 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。