- 您現在的位置:買賣IC網 > PDF目錄383295 > M368L3313DTL-CB3 (SAMSUNG SEMICONDUCTOR CO. LTD.) 256MB DDR SDRAM MODULE (32Mx64(16Mx64*2 bank) based on 16Mx8 DDR SDRAM) PDF資料下載

參數資料

| 型號: | M368L3313DTL-CB3 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 256MB DDR SDRAM MODULE (32Mx64(16Mx64*2 bank) based on 16Mx8 DDR SDRAM) |

| 中文描述: | 256MB的DDR SDRAM內存模塊(32Mx64(16Mx64 * 2銀行)的基礎上16Mx8 DDR內存) |

| 文件頁數: | 6/12頁 |

| 文件大?。?/td> | 99K |

| 代理商: | M368L3313DTL-CB3 |

M368L3313DTL

Rev. 0.2 May.2002

184pin Unbuffered DDR SDRAM MODULE

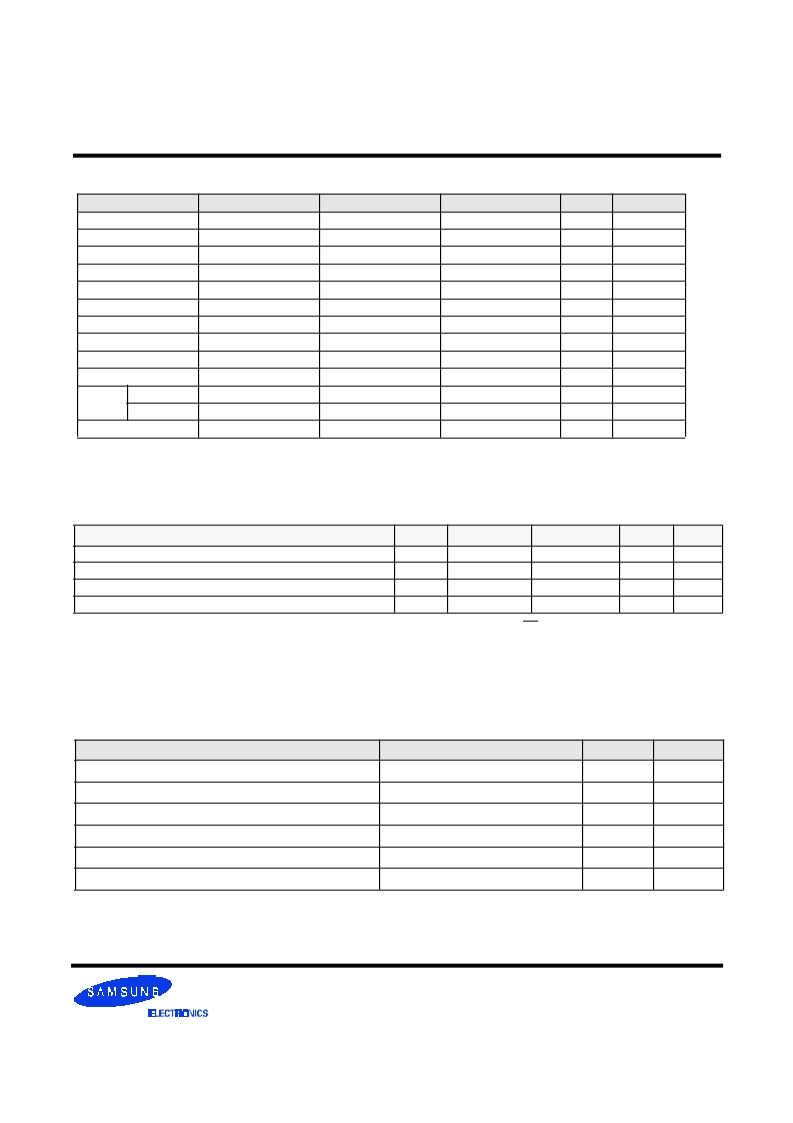

DDR SDRAM IDD spec table

* Module IDD was calculated on the basis of component IDD and can be differently measured according to DQ loading cap.

Symbol

B3(DDR333@CL=2.5)

A2(DDR266@CL=2)

B0(DDR266@CL=2.5)

Unit

Notes

IDD0

1320

1200

1200

mA

IDD1

1520

1400

1400

mA

IDD2P

48

48

48

mA

IDD2F

400

352

352

mA

IDD2Q

288

240

240

mA

IDD3P

560

560

560

mA

IDD3N

960

880

880

mA

IDD4R

1760

1576

1576

mA

IDD4W

1696

1480

1480

mA

IDD5

2000

1880

1880

mA

IDD6

Normal

32

32

32

mA

Low power

16

16

16

mA

Optional

IDD7A

3120

2840

2840

mA

AC OPERATING CONDITIONS

Parameter/Condition

Symbol

Min

Max

Unit

Note

Input High (Logic 1) Voltage, DQ, DQS and DM signals

Input Low (Logic 0) Voltage, DQ, DQS and DM signals.

VIH(AC)

VIL(AC)

VREF + 0.31

V

V

3

3

VREF - 0.31

Input Differential Voltage, CK and CK inputs

VID(AC)

0.7

VDDQ+0.6

V

1

Input Crossing Point Voltage, CK and CK inputs

VIX(AC)

0.5*VDDQ-0.2

0.5*VDDQ+0.2

V

2

Note 1. VID is the magnitude of the difference between the input level on CK and the input on CK.

2. The value of V

IX

is expected to equal 0.5*V

DDQ

of the transmitting device and must track variations in the DC level of the same.

3. These parameters should be tested at the pim on actual components and may be checked at either the pin or the pad in simula-

tion. the AC and DC input specificatims are refation to a Vref envelope that has been bandwidth limited 20MHz.

AC OPERATING TEST CONDITIONS

(V

DD

=2.5V, V

DDQ

=2.5V, T

A

= 0 to 70

°

C

)

Parameter

Value

Unit

Note

Input reference voltage for Clock

0.5 * VDDQ

V

Input signal maximum peak swing

1.5

V

Input Levels(VIH/VIL)

VREF+0.31/VREF-0.31

V

Input timing measurement reference level

VREF

V

Output timing measurement reference level

Vtt

V

Output load condition

See Load Circuit

相關PDF資料 |

PDF描述 |

|---|---|

| M368L6423ETM-CC5 | 184pin Unbuffered Module based on 256Mb E-die 64/72-bit ECC/Non ECC |

| M368L6423FTN | 184pin Unbuffered Module based on 256Mb F-die with 64/72-bit Non-ECC / ECC |

| M368L6423FTN-CB3B0 | 184pin Unbuffered Module based on 256Mb F-die with 64/72-bit Non-ECC / ECC |

| M368L6423DTM-CCC | 184pin Unbuffered Module based on 256Mb D-die 64/72-bit Non ECC/ECC |

| M368L6423DTM-LCC | 184pin Unbuffered Module based on 256Mb D-die 64/72-bit Non ECC/ECC |

相關代理商/技術參數 |

參數描述 |

|---|---|

| M368L3324BT | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Unbuffered Module 184pin Unbuffered Module based on 512Mb B-die with 64/72-bit Non ECC/ECC 66 TSOP-II |

| M368L3324BTM-CB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Unbuffered Module 184pin Unbuffered Module based on 512Mb B-die with 64/72-bit Non ECC/ECC 66 TSOP-II |

| M368L3324BTM-CCC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Unbuffered Module 184pin Unbuffered Module based on 512Mb B-die with 64/72-bit Non ECC/ECC 66 TSOP-II |

| M368L3324BTM-LB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Unbuffered Module 184pin Unbuffered Module based on 512Mb B-die with 64/72-bit Non ECC/ECC 66 TSOP-II |

| M368L3324BTM-LCC | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:DDR SDRAM Unbuffered Module 184pin Unbuffered Module based on 512Mb B-die with 64/72-bit Non ECC/ECC 66 TSOP-II |

發(fā)布緊急采購,3分鐘左右您將得到回復。