- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383295 > M368L1713CTL (SAMSUNG SEMICONDUCTOR CO. LTD.) 128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity PDF資料下載

參數(shù)資料

| 型號(hào): | M368L1713CTL |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| 中文描述: | 128MB DDR SDRAM的模組(16Mx64基于16Mx8 DDR內(nèi)存)緩沖184Pin DIMM插槽64位Non-ECC/Parity |

| 文件頁數(shù): | 8/12頁 |

| 文件大?。?/td> | 83K |

| 代理商: | M368L1713CTL |

184pin Unbuffered DDR SDRAM MODULE

M368L1713CTL

Rev. 0.3 May. 2002

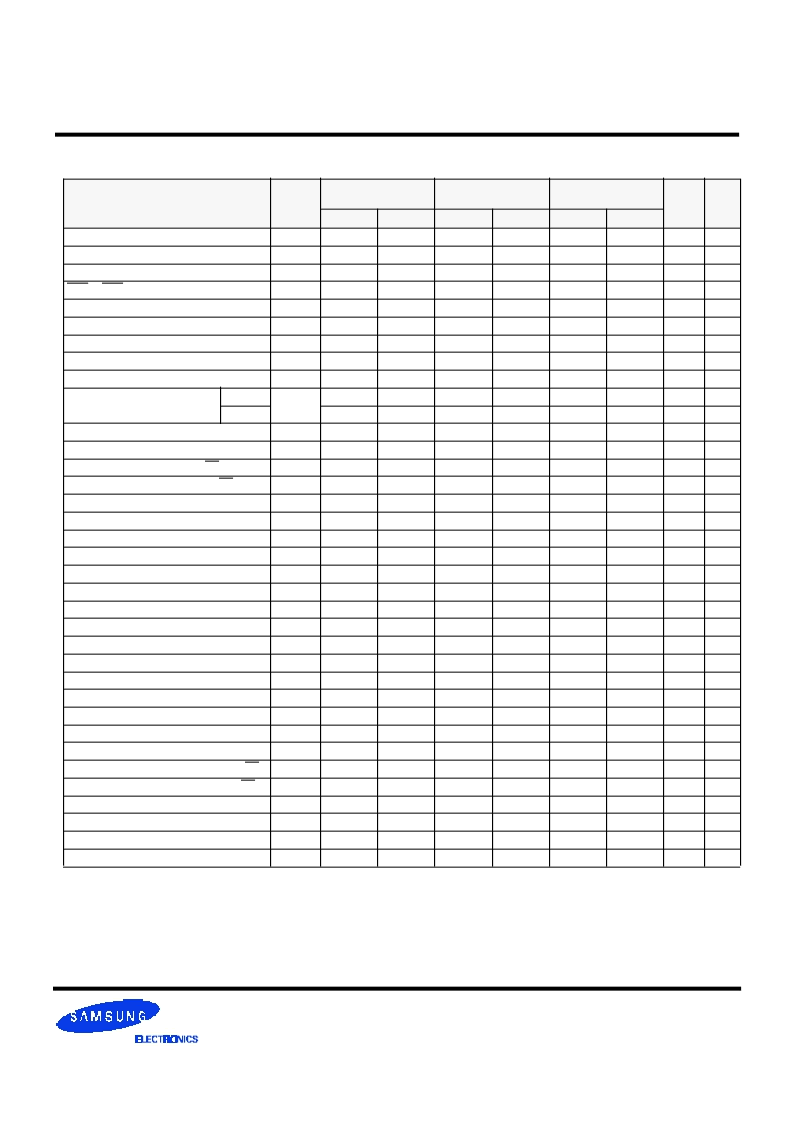

AC Timming Parameters & Specifications

(These AC charicteristics were tested on the Component)

-TCB3

(DDR333)

Parameter

Symbol

-TCA2

(DDR266A)

-TCB0

(DDR266B)

Unit

Note

Min

Max

Min

Max

Min

Max

Row cycle time

tRC

60

65

65

ns

Refresh row cycle time

tRFC

72

75

75

ns

Row active time

tRAS

42

70K

45

120K

45

120K

ns

RAS to CAS delay

tRCD

18

20

20

ns

Row precharge time

tRP

18

20

20

ns

Row active to Row active delay

tRRD

12

15

15

ns

Write recovery time

tWR

15

15

15

ns

Last data in to Read command

tWTR

1

1

1

tCK

Col. address to Col. address delay

tCCD

1

1

1

tCK

Clock cycle time

CL=2.0

tCK

7.5

12

7.5

12

10

12

ns

5

CL=2.5

6

12

7.5

12

7.5

12

ns

5

Clock high level width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Clock low level width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

tCK

DQS-out access time from CK/CK

tDQSCK

-0.6

+0.6

-0.75

+0.75

-0.75

+0.75

ns

Output data access time from CK/CK

tAC

-0.7

+0.7

-0.75

+0.75

-0.75

+0.75

ns

Data strobe edge to ouput data edge

tDQSQ

-

0.45

-

0.5

-

0.5

ns

5

Read Preamble

tRPRE

0.9

1.1

0.9

1.1

0.9

1.1

tCK

Read Postamble

tRPST

0.4

0.6

0.4

0.6

0.4

0.6

tCK

CK to valid DQS-in

tDQSS

0.75

1.25

0.75

1.25

0.75

1.25

tCK

DQS-in setup time

tWPRES

0

0

0

ns

2

DQS-in hold time

tWPRE

0.25

0.25

0.25

tCK

DQS falling edge to CK rising-setup time

tDSS

0.2

0.2

0.2

tCK

DQS falling edge from CK rising-hold time

tDSH

0.2

0.2

0.2

tCK

DQS-in high level width

tDQSH

0.35

0.35

0.35

tCK

DQS-in low level width

tDQSL

0.35

0.35

0.35

tCK

DQS-in cycle time

tDSC

0.9

1.1

0.9

1.1

0.9

1.1

tCK

Address and Control Input setup time(fast)

tIS

0.75

0.9

0.9

ns

6

Address and Control Input hold time(fast)

tIH

0.75

0.9

0.9

ns

6

Address and Control Input setup time(slow)

tIS

0.8

1.0

1.0

ns

6

Address and Control Input hold time(slow)

tIH

0.8

1.0

1.0

ns

6

Data-out high impedence time from CK/CK

tHZ

-0.7

+0.7

-0.75

+0.75

-0.75

+0.75

ns

Data-out low impedence time from CK/CK

tLZ

-0.7

+0.7

-0.75

+0.75

-0.75

+0.75

ns

Input Slew Rate(for input only pins)

tSL(I)

0.5

0.5

0.5

V/ns

6

Input Slew Rate(for I/O pins)

tSL(IO)

0.5

0.5

0.5

V/ns

7

Output Slew Rate(x4,x8)

tSL(O)

1.0

4.5

1.0

4.5

1.0

4.5

V/ns

10

Output Slew Rate Matching Ratio(rise to fall)

tSLMR

0.67

1.5

0.67

1.5

0.67

1.5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M368L1713CTL-CA2 | 128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-CB0 | 128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-CB3 | 128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L3313DTL | 256MB DDR SDRAM MODULE (32Mx64(16Mx64*2 bank) based on 16Mx8 DDR SDRAM) |

| M368L3313DTL-CA2 | 256MB DDR SDRAM MODULE (32Mx64(16Mx64*2 bank) based on 16Mx8 DDR SDRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M368L1713CTL-CA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-CB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-CB3 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-LA2 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

| M368L1713CTL-LB0 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:128MB DDR SDRAM MODULE (16Mx64 based on 16Mx8 DDR SDRAM) Unbuffered 184pin DIMM 64-bit Non-ECC/Parity |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。