- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359055 > M34C02-LDW6T (意法半導(dǎo)體) 2 Kbit Serial IC Bus EEPROM For DIMM Serial Presence Detect PDF資料下載

參數(shù)資料

| 型號(hào): | M34C02-LDW6T |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | 2 Kbit Serial IC Bus EEPROM For DIMM Serial Presence Detect |

| 中文描述: | 2千位串行IC總線的EEPROM內(nèi)存串行存在檢測(cè) |

| 文件頁(yè)數(shù): | 6/19頁(yè) |

| 文件大小: | 147K |

| 代理商: | M34C02-LDW6T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

M34C02

6/19

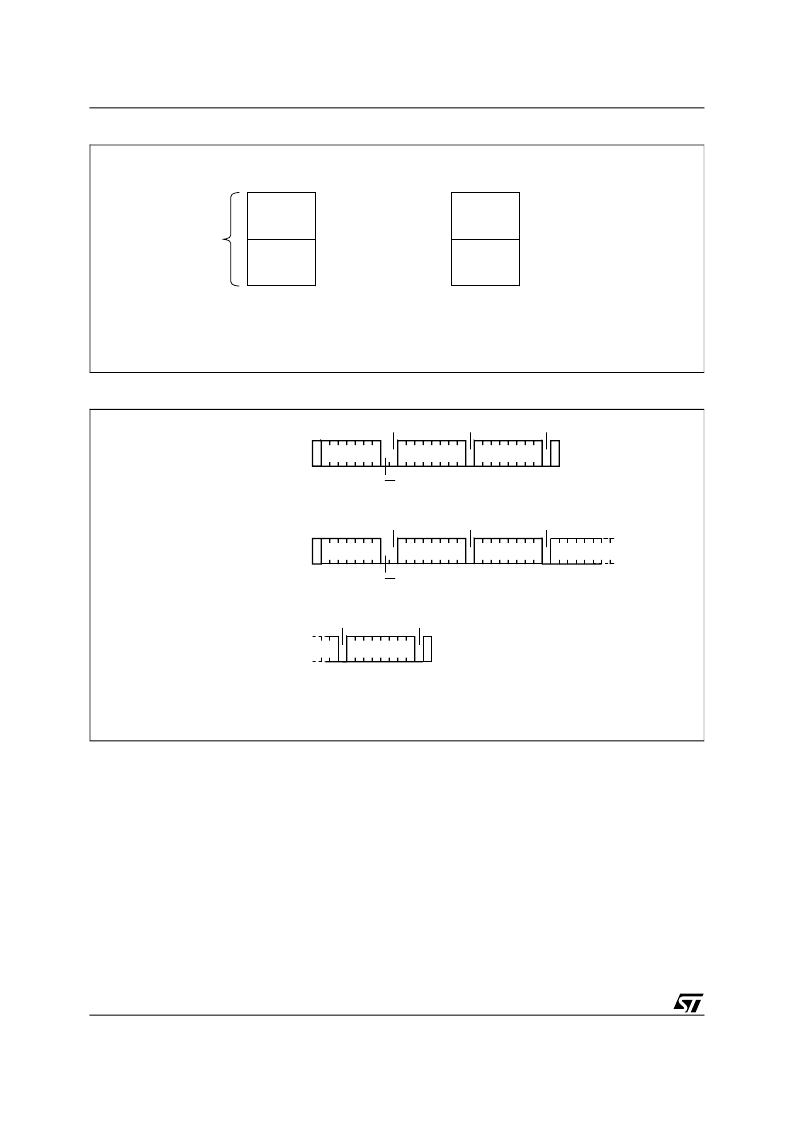

Figure 5. How to Set the Write Protection

Figure 6. Write Mode Sequences in the Non Write-Protected Area

Default EEPROM memory area

state before write access

to the Protect Register

AI01936C

Standard

Array

FFh

Standard

Array

80h

7Fh

00h

Standard

Array

FFh

Write

Protected

Array

80h

7Fh

00h

State of the EEPROM memory

area after write access

to the Protect Register

Memory

Area

S

S

BYTE WRITE

DEV SEL

BYTE ADDR

DATA IN

S

PAGE WRITE

DEV SEL

BYTE ADDR

DATA IN 1

DATA IN 2

AI01941

S

DATA IN N

ACK

ACK

ACK

R/W

ACK

ACK

ACK

R/W

ACK

ACK

significant bits only) is incremented. The transfer is

terminated by the master generating a STOP

condition.

When the master generates a STOP condition

immediately after the Ack bit (in the “10

th

bit” time

slot), either at the end of a byte write or a page

write, the internal memory write cycle is triggered.

A STOP condition at any other time does not

trigger the internal write cycle.

During the internal write cycle, the SDA input is

disabled internally, and the device does not

respond to any requests.

Minimizing System Delays by Polling On ACK

During the internal write cycle, the memory

disconnects itself from the bus, and copies the

data from its internal latches to the memory cells.

The maximum write time (t

w

) is shown in Table 9,

but the typical time is shorter. To make use of this,

an Ack polling sequence can be used by the

master.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34D64MNT6 | 64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64WMNT1 | 64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64WMNT5 | 64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64MN | 64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

| M34D64RBNT5 | 64/32 Kbit Serial IC Bus EEPROM With Hardware Write Control on Top Quarter of Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34C02-LDW6TG | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:2 Kbit Serial IC Bus EEPROM for DIMM serial presence detect |

| M34C02-LDW6TP | 功能描述:電可擦除可編程只讀存儲(chǔ)器 2.2-5.5V 2K (256x8) RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M34C02-LMB1G | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:2 Kbit Serial IC Bus EEPROM for DIMM serial presence detect |

| M34C02-LMB1P | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:2 Kbit Serial IC Bus EEPROM for DIMM serial presence detect |

| M34C02-LMB1TG | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:2 Kbit Serial IC Bus EEPROM for DIMM serial presence detect |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。