- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370837 > M34250M2-066FP (Mitsubishi Electric Corporation) SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M34250M2-066FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單芯片4位微機(jī)的CMOS |

| 文件頁(yè)數(shù): | 17/58頁(yè) |

| 文件大?。?/td> | 331K |

| 代理商: | M34250M2-066FP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)當(dāng)前第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)

MITSUBISHI

ELECTRIC

17

MITSUBISHI MICROCOMPUTERS

4250 Group

SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

(6) Control register related to interrupt

Timer control register V1

Interrupt enable bits of external and timer 1 are assigned

to register V1. Set the contents of this register through

register A with the TV1A instruction. The TAV1 instruction

can be used to transfer the contents of register V1 to register

A.

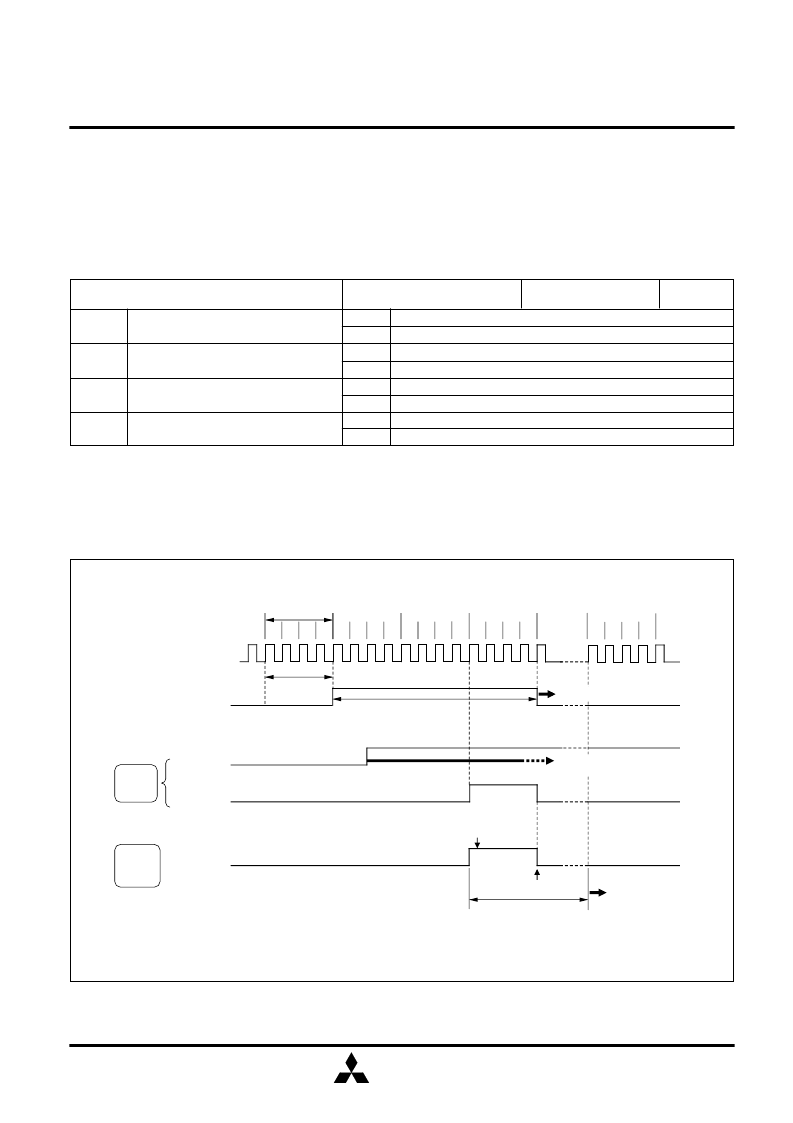

(7) Interrupt sequence

Interrupts occur only when the respective INTE flag, interrupt

enable bits (V1

0

, V1

1

), and interrupt request flags (EXF0, T1F)

are “1.” The interrupt actually occurs 2 to 3 machine cycles

after the cycle in which all three conditions are satisfied. The

interrupt occurs after 3 machine cycles only when the three

interrupt conditions are satisfied on execution of other than

one-cycle instructions (Refer to Figure 16).

Fig. 16 Interrupt sequence

Table 6 Control register related to interrupt

V1

3

V1

2

V1

1

V1

0

Timer control register V1

G

1

/T

OUT

pin function selection bit

Prescaler/timer 1 operation start bit

Timer 1 interrupt enable bit

External interrupt enable bit

Port G

1

(I/O)

T

OUT

pin (output)/port G

1

(input)

Prescaler stop (initial state) / timer 1 stop (state retained)

Prescaler / timer 1 operation

Interrupt disabled (SNZ1 instruction is valid)

Interrupt enabled (SNZ1 instruction is invalid)

Interrupt disabled (SNZ0 instruction is valid)

Interrupt enabled (SNZ0 instruction is invalid)

0

1

0

1

0

1

0

1

Note: “R” represents read enabled, and “W” represents write enabled.

at reset : 0000

2

R/W

at RAM back-up : 0000

2

T

1

T

2

T

3

T

4

T

1

T

2

T

3

T

4

T

1

T

2

T

3

T

4

T

1

T

2

T

3

T

4

T

1

T

2

T

3

T

4

2

to 3

machine cycles

(Notes 1, 2)

Software starts from

the interrupt address.

Flag cleared

Interrupt enabled state.

G

When an interrupt request flag is set after its interrupt is enabled

f (X

IN

)

EI instruction

execution cycle

Interrupt enable

flag (INTE)

Retaining level for 5 cycles or more

of f(X

IN

) is necessary.

Interrupt disabled state.

EXF0

flag

T1F flag

G

0

/INT pin

External

interrupt

Timer 1

interrupt

Interrupt activated

condition is satisfied.

1 machine cycle

The address is stacked to the last cycle.

This interval of cycles depends on the executed instruction at the time when each interrupt activated condition is satisfied.

Notes 1:

2:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M34250M2-086FP | SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250M2-099FP | SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250M2-116FP | SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250 | Single Chip 4 Bits CMOS Microcomputer(4位單片機(jī)) |

| M34250E2FP | SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M34250M2-086FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250M2-099FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250M2-116FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M34250M2-XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER |

| M3426 SL002 | 制造商:Alpha Wire 功能描述:CBL 8PR 24AWG SLT 500' |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。