- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359000 > M27V402-120F6TR (意法半導(dǎo)體) Quadruple 2-Input Positive-NAND Gates 14-SO 0 to 70 PDF資料下載

參數(shù)資料

| 型號: | M27V402-120F6TR |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Quadruple 2-Input Positive-NAND Gates 14-SO 0 to 70 |

| 中文描述: | 4兆位的256Kb × 16低壓紫外線存儲(chǔ)器和OTP存儲(chǔ)器 |

| 文件頁數(shù): | 2/15頁 |

| 文件大?。?/td> | 101K |

| 代理商: | M27V402-120F6TR |

M27V402

2/15

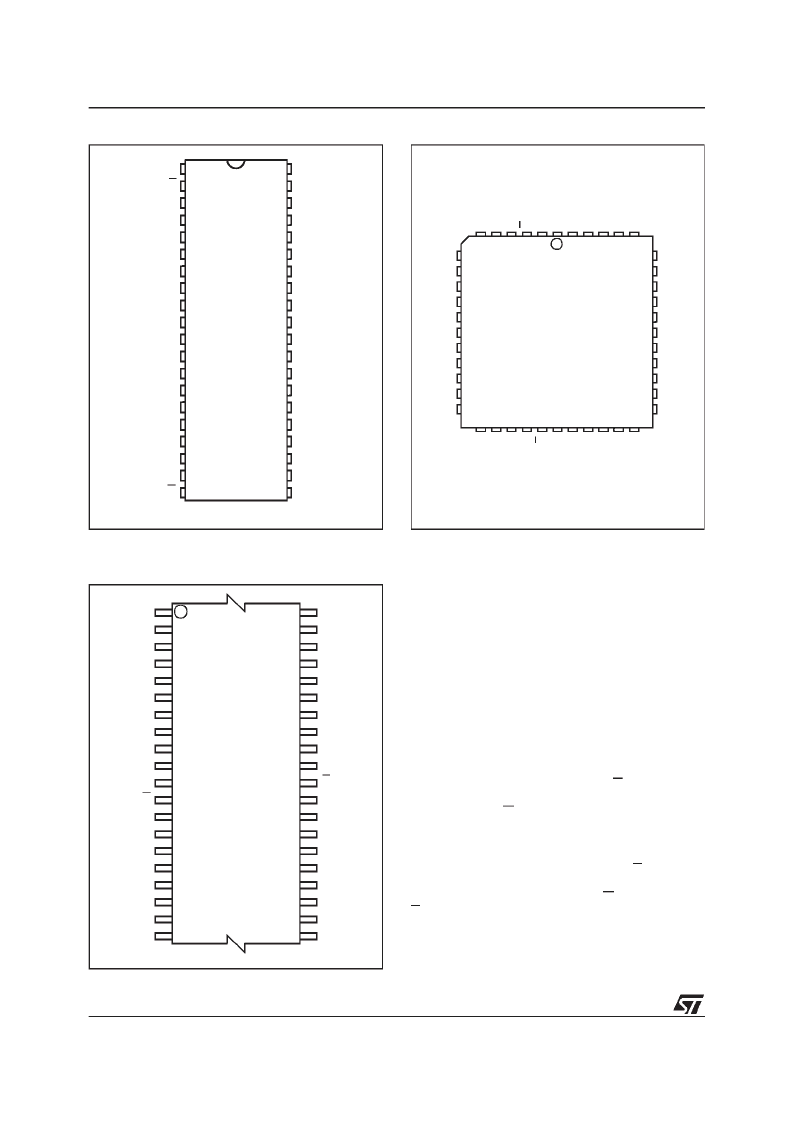

Figure 2B. LCC Pin Connections

Warning

: NC = Not Connected.

AI01820

A

A11

A10

A7

A6

A

23

Q6

Q5

Q4

Q

Q

N

A

Q12

Q11

Q10

Q9

Q8

VSS

NC

Q7

12

A

A9

VSS

NC

A8

1

Q

A12

Q

A5

44

N

A

M27V402

Q

A13

A

34

Q

Q

G

A

A

V

E

A

V

Figure 2A. DIP Pin Connections

Q6

Q5

Q4

Q3

Q2

Q11

Q10

Q9

Q8

VSS

Q7

A12

A11

A10

A9

VSS

A8

A7

A6

A5

A4

A3

A13

A2

A1

Q1

Q0

G

A0

A16

A15

A17

E

Q12

VPP

VCC

Q15

Q14

Q13

AI01862

M27V402

8

9

10

11

12

13

14

15

16

17

1

2

3

4

5

6

7

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

40

39

38

37

36

35

34

33

A14

For applications wherethe content is programmed

only one time and erasure is not required, the

M27V256 is offered in PDIP40, PLCC44 and

TSOP40 (10 x 20 mm) packages.

DEVICE OPERATION

The operating modes of the M27V402 are listed in

the Operating Modes table. A single power supply

is required in the read mode. All inputs are TTL

levels except for V

PP

and 12V on A9 for Electronic

Signature.

Read Mode

The M27V402 has two control functions, both of

which must be logically active in order to obtain

data at the outputs. Chip Enable (E) is the power

control and should be used for device selection.

Output Enable (G) is the output control and should

be used to gate data to the output pins,

independent of device selection. Assuming that

the addresses are stable, the address access time

(t

AVQV

) is equal to the delay from E to output

(t

ELQV

). Datais available atthe output aftera delay

of t

GLQV

from the falling edge of G, assuming that

E has been low and the addresses have been

stable for at least t

AVQV

-t

GLQV

.

Figure 2C. TSOP Pin Connections

DQ6

DQ7

VSS

DQ3

DQ4

DQ2

DQ13

DQ12

DQ8

DQ10

DQ9

A14

A15

A16

A17

VCC

A8

A7

A6

A5

A11

A12

A10

A4

A3

A9

G

DQ0

A2

A1

DQ1

A0

E

DQ14

VPP

DQ15

AI01821

M27V402

(Normal)

10

11

1

20

21

30

31

40

A13

DQ11

DQ5

VSS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M27V402-120K1TR | 4 Mbit 256Kb x 16 Low Voltage UV EPROM and OTP EPROM |

| M27V402-120K4TR | Quadruple 2-Input Positive-NOR Gates 14-SOIC 0 to 70 |

| M27V402-120K5TR | 4 Mbit 256Kb x 16 Low Voltage UV EPROM and OTP EPROM |

| M27V402-120K6TR | 4 Mbit 256Kb x 16 Low Voltage UV EPROM and OTP EPROM |

| M27V402-120N1TR | Quadruple 2-Input Positive-NOR Gates 14-PDIP 0 to 70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M27V402-120K1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x 8 Low Voltage OTP EPROM |

| M27V402-120K4TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x 8 Low Voltage OTP EPROM |

| M27V402-120K5TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x 8 Low Voltage OTP EPROM |

| M27V402-120K6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x 8 Low Voltage OTP EPROM |

| M27V402-120N1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:4 Mbit 512Kb x 8 Low Voltage OTP EPROM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。