- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄358969 > M24128-BWMN6TP (意法半導(dǎo)體) Displays PDF資料下載

參數(shù)資料

| 型號(hào): | M24128-BWMN6TP |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | Displays |

| 中文描述: | 256Kbit和128Kbit的EEPROM串行I2C總線具有三個(gè)芯片使能線 |

| 文件頁(yè)數(shù): | 10/17頁(yè) |

| 文件大小: | 135K |

| 代理商: | M24128-BWMN6TP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

M24256, M24128

10/17

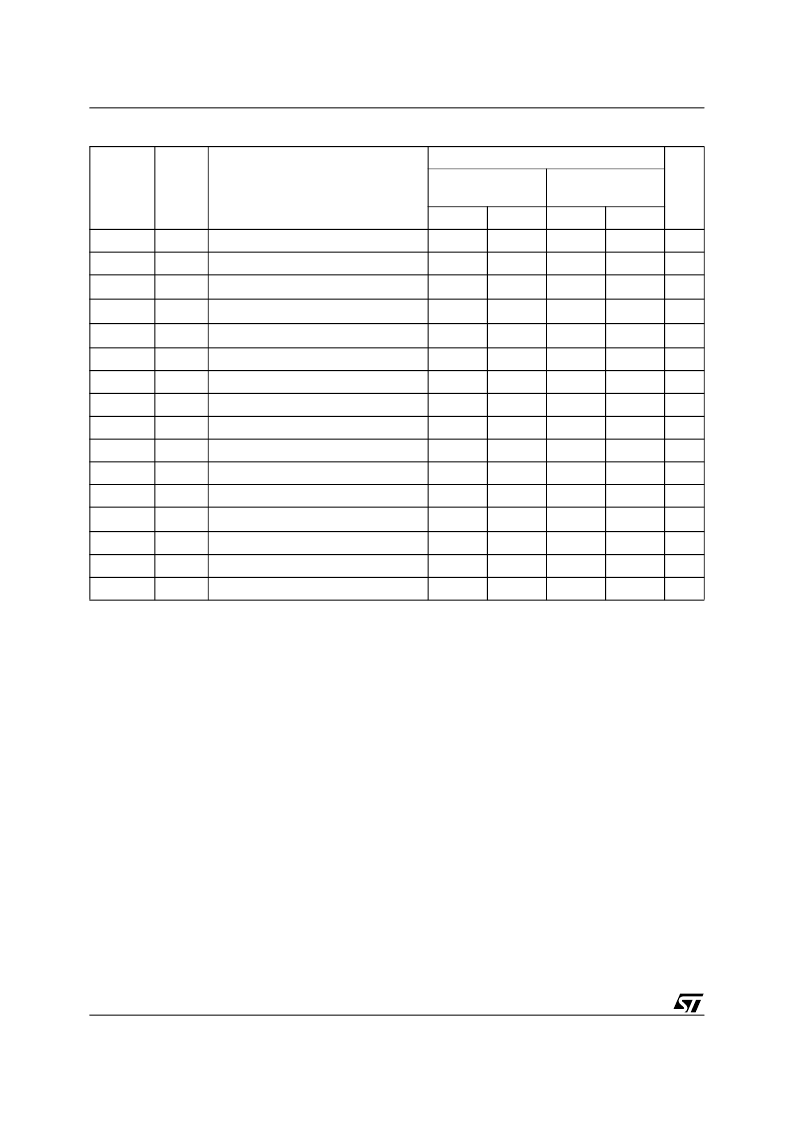

Table 10. AC Characteristics

Note: 1. For a reSTART condition, or following a write cycle.

2. Sampled only, not 100% tested.

3. To avoid spurious START and STOP conditions, a minimum delay is placed between SCL=1 and the falling or rising edge of SDA.

Symbol

Alt.

Parameter

M24256 / M24128

Unit

V

CC

=4.5 to 5.5 V

T

A

=–40 to 85°C

V

CC

=2.5 to 5.5 V

T

A

=–40 to 85°C

Min

Max

Min

Max

t

CH1CH2

t

R

Clock Rise Time

300

300

ns

t

CL1CL2

t

F

Clock Fall Time

300

300

ns

t

DH1DH2 2

t

R

SDA Rise Time

20

300

20

300

ns

t

DL1DL2 2

t

F

SDA Fall Time

20

300

20

300

ns

t

CHDX 1

t

SU:STA

Clock High to Input Transition

600

600

ns

t

CHCL

t

HIGH

Clock Pulse Width High

600

600

ns

t

DLCL

t

HD:STA

Input Low to Clock Low (START)

600

600

ns

t

CLDX

t

HD:DAT

Clock Low to Input Transition

0

0

μs

t

CLCH

t

LOW

Clock Pulse Width Low

1.3

1.3

μs

t

DXCX

t

SU:DAT

Input Transition to Clock Transition

100

100

ns

t

CHDH

t

SU:STO

Clock High to Input High (STOP)

600

600

ns

t

DHDL

t

BUF

Input High to Input Low (Bus Free)

1.3

1.3

μs

t

CLQV 3

t

AA

Clock Low to Data Out Valid

200

900

200

900

ns

t

CLQX

t

DH

Data Out Hold Time After Clock Low

200

200

ns

f

C

f

SCL

Clock Frequency

400

400

kHz

t

W

t

WR

Write Time

10

10

ms

cremented. The master terminates the transfer

with a STOP condition, as shown in Figure 8, with-

out acknowledging the byte output.

Sequential Read

This mode can be initiated with either a Current

Address Read or a Random Address Read. The

master does acknowledge the data byte output in

this case, and the memory continues to output the

next byte in sequence. To terminate the stream of

bytes, the master must notacknowledge the last

byte output, and mustgenerate a STOP condition.

The output data comes from consecutive address-

es, with the internal address counter automatically

incremented after each byte output. After the last

memory address, the address counter ‘rolls-over’

and the memory continues to output data from

memory address 00h.

Acknowledge in Read Mode

In all read modes, the memory waits, after each

byte read, for an acknowledgment during the 9

th

bit time. If the master does not pull the SDA line

low during this time, the memory terminates the

data transfer and switches to its stand-by state.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M24128-BWBN6T | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWBN6P | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWBN6G | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWBN6 | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6TG | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M24128-BWMN6TP-CUT TAPE | 制造商:ST 功能描述:M24128 Series 128 Kb (16 K x 8) 2.5 V SMT 2 Wire Serial I? EEPROM - SOIC-8 |

| M24128-BWMW16T | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:256/128 Kbit Serial IC Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6 | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6G | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6P | 制造商:STMICROELECTRONICS 制造商全稱(chēng):STMicroelectronics 功能描述:256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。