- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358970 > M24128-BWMN6TG (意法半導體) 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines PDF資料下載

參數(shù)資料

| 型號: | M24128-BWMN6TG |

| 廠商: | 意法半導體 |

| 元件分類: | DRAM |

| 英文描述: | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| 中文描述: | 256Kbit和128Kbit的EEPROM串行I2C總線具有三個芯片使能線 |

| 文件頁數(shù): | 6/17頁 |

| 文件大小: | 135K |

| 代理商: | M24128-BWMN6TG |

M24256, M24128

6/17

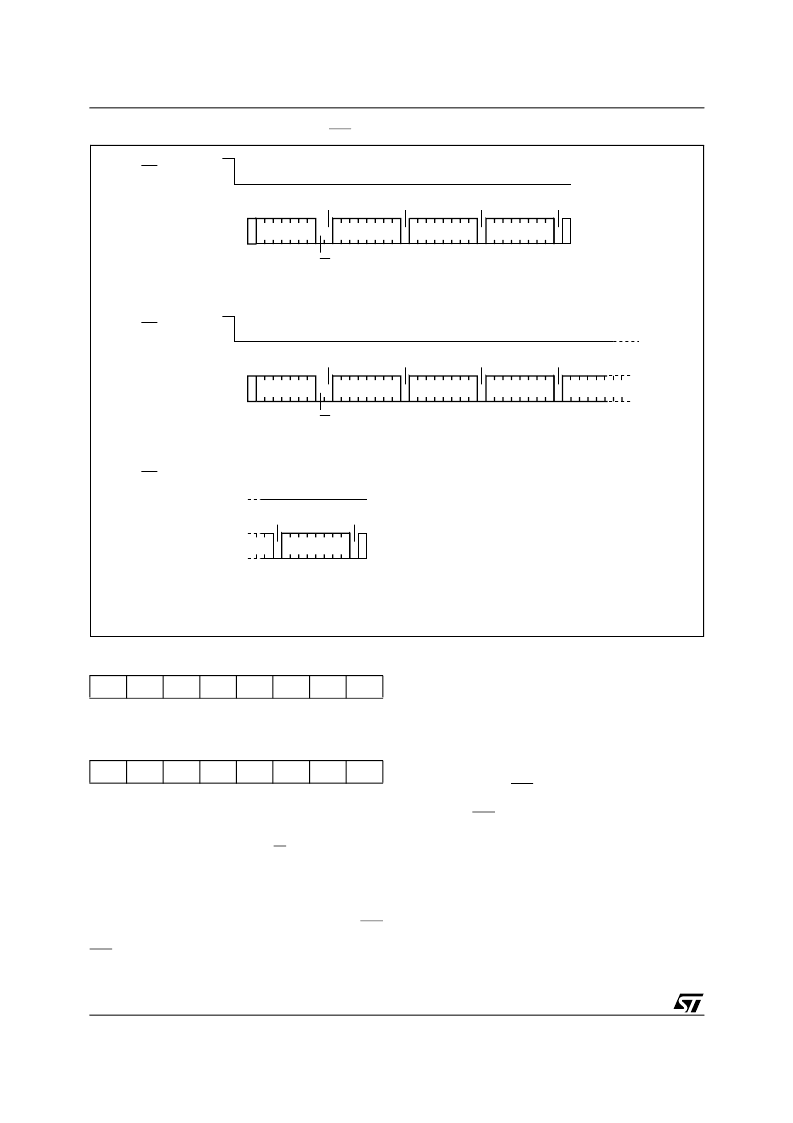

Figure 6. Write Mode Sequences with WC=0 (data write enabled)

S

S

BYTE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN

WC

S

PAGE WRITE

DEV SEL

BYTE ADDR

BYTE ADDR

DATA IN 1

WC

DATA IN 2

AI01106B

PAGE WRITE

(cont'd)

WC (cont'd)

S

DATA IN N

ACK

R/W

ACK

ACK

ACK

ACK

ACK

ACK

ACK

R/W

ACK

ACK

Write Operations

Following a START condition the master sends a

Device Select Code with the RW

bit set to ’0’, as

shown in Table 4. The memory acknowledges this,

and waits for two address bytes. The memory re-

sponds to each address byte with an acknowledge

bit, and then waits for the data byte.

Writing to the memory may be inhibited if the WC

input pin is taken high. Any write command with

WC=1 (during a period of time from the START

condition until the end of the two address bytes)

will not modify the memory contents, and the ac-

companying data bytes will

not

be acknowledged,

as shown in Figure 5.

Byte Write

In the Byte Write mode, after the Device Select

Code and the address bytes, the master sends

one data byte. If the addressed location is write

protected by the WC pin, the memory replies with

a NoAck, and the location is not modified. If, in-

stead, the WC pin has been held at 0, as shown in

Figure 6, the memory replies with an Ack. The

master terminates the transfer by generating a

STOP condition.

Page Write

The Page Write mode allows up to 64 bytes to be

written in a single write cycle, provided that they

are all located in the same ’row’ in the memory:

that is the most significant memory address bits

(b14-b6 for the M24256 and b13-b6 for the

M24128) are the same. If more bytes are sent than

Table 5. Most Significant Byte

Note: 1.

b15 is treated as Don’t Care on the M24256 series.

b15 and b14 are Don’t Care on the M24128 series.

Table 6. Least Significant Byte

b15

b14

b13

b12

b11

b10

b9

b8

b7

b6

b5

b4

b3

b2

b1

b0

相關PDF資料 |

PDF描述 |

|---|---|

| M24128-BWMN6T | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMN6P | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMN6G | 3W1-ETM-230/60HZ W/BLACK DIAL MOD METER - Jewell / Modutech SP W/LDS,00-139002-102 |

| M24128-BWMN6 | 256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWBN6TG | INDUCTOR 1.6X0.8X0.8MM 2.2NH |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| M24128-BWMN6TP | 功能描述:電可擦除可編程只讀存儲器 128K (16Kx8) RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| M24128-BWMN6TP-CUT TAPE | 制造商:ST 功能描述:M24128 Series 128 Kb (16 K x 8) 2.5 V SMT 2 Wire Serial I? EEPROM - SOIC-8 |

| M24128-BWMW16T | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256/128 Kbit Serial IC Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

| M24128-BWMW6G | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:256Kbit and 128Kbit Serial I2C Bus EEPROM With Three Chip Enable Lines |

發(fā)布緊急采購,3分鐘左右您將得到回復。