- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4478 > M1A3P600-PQG208I (Microsemi SoC)IC FPGA 1KB FLASH 600K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | M1A3P600-PQG208I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 9/12頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1KB FLASH 600K 208-PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | ProASIC3 |

| RAM 位總計: | 110592 |

| 輸入/輸出數(shù): | 154 |

| 門數(shù): | 600000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

ARM CortexTM-M1

6P ro d u c t B r i e f

stack. You can access the APSR with the MSR and

MRS instructions.

Interrupt PSR (IPSR) – Contains the Interrupt

Service Routine (ISR) number of the current

exception activation.

Execution PSR (EPSR) – Contains the Thumb state

bit (T-bit). Unless the processor is in Debug state,

the EPSR is not directly accessible. All fields read as

zero using an MRS instruction and MSR instruction

writes are ignored.

On entering an exception, the processor saves the

combined information from the three status registers on

the stack.

Special Purpose Priority Mask Register

Use the special purpose Priority Mask Register for

priority boosting. You can access the special purpose

Priority

Mask

Register

using

the

MSR

and

MRS

instructions. You can also use the CPS instruction to set or

clear PRIMASK.

Special Purpose Control Register

The special purpose Control Register identifies the stack

pointers used.

Data Types

The processor supports the following data types:

32-bit words

16-bit halfwords

8-bit bytes

Note: Unless otherwise stated, the core can access all

regions of the memory map, including the code region,

with all data types. To support this, the system must

support sub-word writes without corrupting neighboring

bytes in that word.

Memory Formats

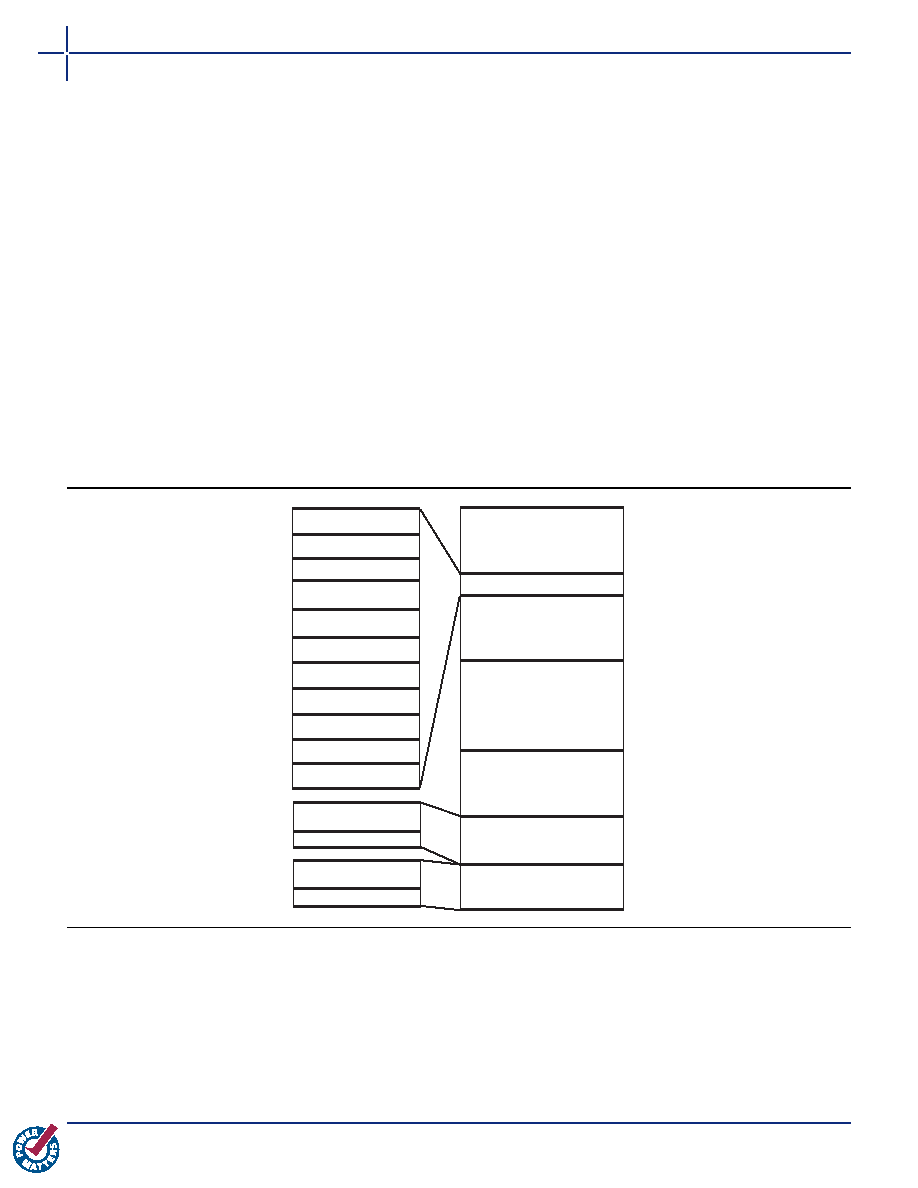

The processor views memory as a linear collection of

bytes numbered in ascending order from 0 (Figure 3).

Figure 3 Processor Memory Map

0xE00FFFFF

0xF00FF000

0xE000ED00

0xE000E000

0xE0003000

0xE0002000

0xE0001000

0xE0000000

0xE000F000

0xE003FFFF

0xE0040000

0xE0041000

0xE0042000

ROM Table

Reserved

BP

DW

Reserved

NVIC

Debug Control

Reserved

0x3FFFFFFF

0x20100000

511 MB

1 MB

511 MB

1 MB

External

DTCM

External

ITCM

0x00100000

0x1FFFFFFF

0x20000000

0x00000000

Reserved

Internal Private Peripheral Bus

1 GB

0.5 GB

Code

SRAM

Peripheral

External

External Device

0.5 GB

0xFFFFFFFF

0xE0100000

0x5FFFFFFF

0x40000000

0x3FFFFFFF

0x20000000

0x1FFFFFFF

0x00000000

0x60000000

0x9FFFFFFF

0xA0000000

0xDFFFFFFF

0x00000000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A40MX02-3VQG80 | IC FPGA MX SGL CHIP 3K 80-VQFP |

| A40MX02-3VQ80 | IC FPGA MX SGL CHIP 3K 80-VQFP |

| FMM18DSEN | CONN EDGECARD 36POS .156 EYELET |

| EP4CE22F17I8L | IC CYCLONE IV FPGA 22K 256FBGA |

| EP4CE22F17I7 | IC CYCLONE IV FPGA 22K 256FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M1A3P600-VQ144 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P600-VQ144ES | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P600-VQ144I | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P600-VQ144PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P600-VQG144 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。