- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4463 > M1A3P1000-FGG144I (Microsemi SoC)IC FPGA M1 1KB FLASH 1M 144FPGA PDF資料下載

參數(shù)資料

| 型號: | M1A3P1000-FGG144I |

| 廠商: | Microsemi SoC |

| 文件頁數(shù): | 8/12頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA M1 1KB FLASH 1M 144FPGA |

| 標(biāo)準(zhǔn)包裝: | 160 |

| 系列: | ProASIC3 |

| RAM 位總計(jì): | 147456 |

| 輸入/輸出數(shù): | 97 |

| 門數(shù): | 1000000 |

| 電源電壓: | 1.425 V ~ 1.575 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 85°C |

| 封裝/外殼: | 144-LBGA |

| 供應(yīng)商設(shè)備封裝: | 144-FPBGA(13x13) |

ARM CortexTM-M1

Prod uct Br ief

5

Programmer’s Model

The ARM Cortex-M1 processor supports all ARMv6-M

Thumb instructions. This includes the entire 16-bit

Thumb instruction set architecture and some 32-bit

instructions.

or

information

on

ARMv6-M

Thumb

instructions, see the ARMv6-M Architecture Reference

Manual.

The

processor

does

not

support

ARM

instructions.

Processor Operating States

The ARM Cortex-M1 processor has two operating states:

Thumb state – This is the normal execution state,

with the processor running the 16-bit and 32-bit

halfword-aligned Thumb and Thumb-2 BL, MRS,

MSR, ISB, DSB, and DMB instructions.

Debug state – This is the state the processor is in

for debugging.

Processor Operating Modes

The ARM Cortex-M1 processor supports two modes of

operation:

Thread mode – Entered on Reset, and can be re-

entered as a result of an exception return.

Handler mode – Entered as a result of an

exception.

Main Stack and Process Stack Access

Out of reset, all code uses the main stack. An exception

handler such as SVC can change the stack used by Thread

mode from main stack to process stack by changing the

EXC_RETURN value it uses on exit. All exceptions

continue to use the main stack. The stack pointer, R13, is

a banked register that switches between the main stack

and the process stack. Only one stack, either the process

stack or the main stack, is visible, using R13, at any time.

It is also possible to switch from the main stack to process

stack while in Thread mode by writing to the special

purpose Control Register using an MSR instruction.

Registers

The

processor

has

the

following

32-bit

registers

13 general purpose registers, R0–R12

Stack Pointer (SP) (SP, R13) and banked register

aliases, SP_process and SP_main

Link Register (LR, R14)

Program Counter (PC, R15)

Program status registers (xPSR)

General Purpose Registers

The general purpose registers, R0–R12, have no special

architecturally-defined uses.

Low registers – Registers R0–R7 are accessible by

all instructions that specify a general purpose

register.

High

registers

–

Registers R8-R12 are not

accessible by all 16-bit instructions.

The R13, R14, and R15 registers have the following

special functions:

Stack Pointer – Register R13 is used as the Stack

Pointer (SP). Because the SP ignores writes to bits

[1:0], it is auto-aligned to a word, four-byte, and

boundary. Handler mode always uses SP_main, but

you can configure Thread mode to use either

SP_main or SP_process.

Link Register – Register R14 is the subroutine

Link Register (LR). The LR receives the return

address from PC when a Branch and Link (BL)

instruction is executed. The LR is also used for an

exception return. At all other times, you can treat

R14 as a general purpose register.

Program Counter – Register R15 is the Program

Counter (PC). Bit 0 is always 0, so instructions are

always aligned to halfword boundaries.

Special Purpose Program Status Registers

(xPSR)

Processor status at the system level breaks down into

three categories and can be accessed as individual

registers, a combination of any two from three, or a

combination of all three, using the MRS and MSR

instructions.

Application PSR (APSR) – Contains the condition

code flags. Before entering an exception, the

processor saves the condition code flags on the

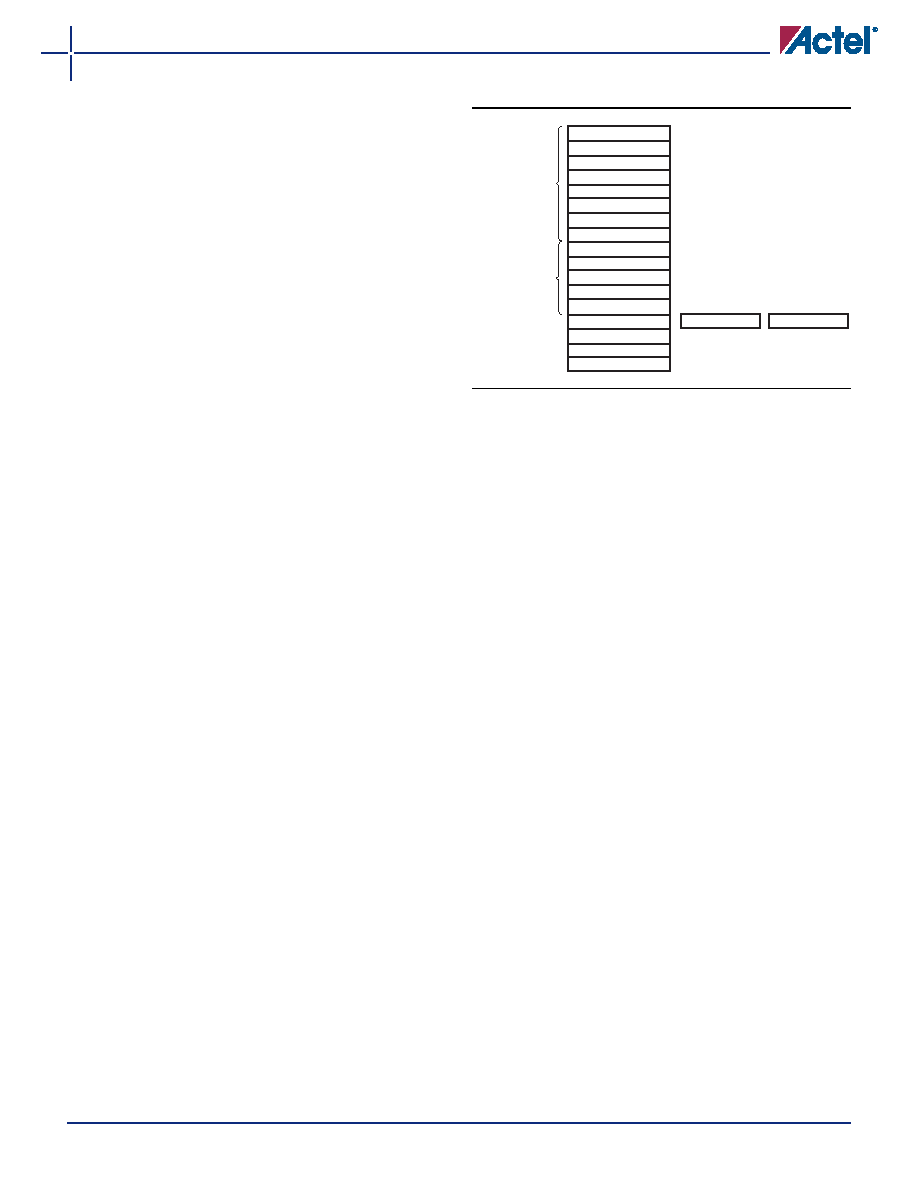

Figure 2 Processor Register Set

r1

r2

r3

r4

r5

r0

High Registers

Low Registers

r9

r10

r11

r12

Program

Status Register

r8

r7

r6

r13 (SP)

r14 (LR)

r15 (PC)

xPSR

SP_main

SP_process

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A3P1000-FGG144I | IC FPGA 1KB FLASH 1M 144-FBGA |

| RMM36DTAD | CONN EDGECARD 72POS R/A .156 SLD |

| A54SX32A-TQG144A | IC FPGA SX 48K GATES 144-TQFP |

| A3PE600-1FGG256I | IC FPGA 600000 GATES 256-FBGA |

| ASM36DRYI | CONN EDGECARD 72POS DIP .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M1A3P1000-FGG144M | 制造商:Microsemi Corporation 功能描述:FPGA PROASIC?3 FAMILY 1M GATES 130NM (CMOS) TECHNOLOGY 1.5V - Trays 制造商:Microsemi Corporation 功能描述:IC FPGA 1M GATES W/M1 144GBGA 制造商:Microsemi Corporation 功能描述:IC FPGA 97 I/O 144GBGA |

| M1A3P1000-FGG144PP | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:ProASIC3 Flash Family FPGAs |

| M1A3P1000-FGG256 | 功能描述:IC FPGA M1 1KB FLASH 1M 256FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標(biāo)準(zhǔn)包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計(jì):36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

| M1A3P1000-FGG256I | 功能描述:IC FPGA M1 1KB FLASH 1M 256FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標(biāo)準(zhǔn)包裝:40 系列:SX-A LAB/CLB數(shù):6036 邏輯元件/單元數(shù):- RAM 位總計(jì):- 輸入/輸出數(shù):360 門數(shù):108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應(yīng)商設(shè)備封裝:484-FPBGA(27X27) |

| M1A3P1000-FGG484 | 功能描述:IC FPGA M1 1KB FLASH 1M 484FBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ProASIC3 標(biāo)準(zhǔn)包裝:90 系列:ProASIC3 LAB/CLB數(shù):- 邏輯元件/單元數(shù):- RAM 位總計(jì):36864 輸入/輸出數(shù):157 門數(shù):250000 電源電壓:1.425 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 125°C 封裝/外殼:256-LBGA 供應(yīng)商設(shè)備封裝:256-FPBGA(17x17) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。