- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9785HC LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT9785HC |

| 英文描述: | LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|八路| QFP封裝| 208PIN |塑料 |

| 文件頁數(shù): | 61/68頁 |

| 文件大小: | 1177K |

| 代理商: | LXT9785HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

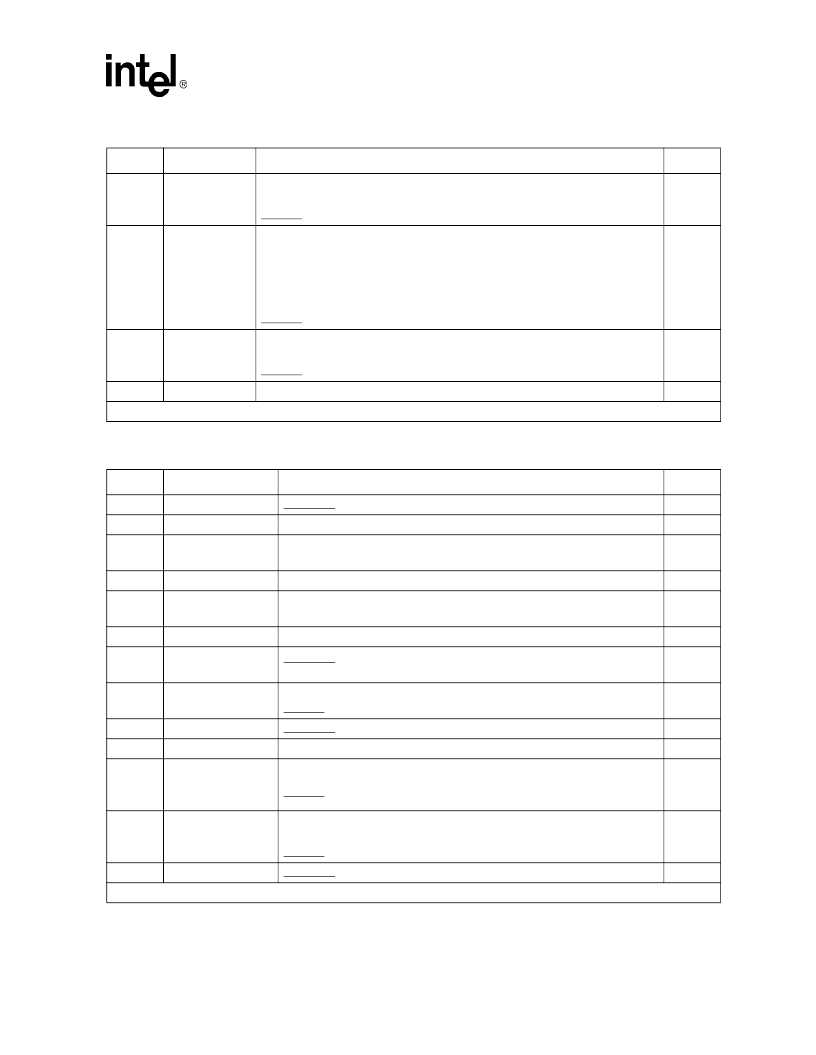

Low-Power Octal PHY

—

LXT9784

Datasheet

61

0.9

Restart Auto-

Negotiation

Restarts the auto-negotiation process and is self cleared after 300 ns

1 = Restart auto-negotiation process.

default 0 = normal operation.

RW

SC

0.8

Duplex Mode

Controls the duplex mode when auto-negotiation is disabled. If the PHY reports that

it only able to operate in one duplex mode (via bits 1.15:11), the value of this bit shall

correspond to the mode which the PHY can operate.

When the PHY is placed in Loopback mode, the behavior of the PHY shall not be

affected by the status of this bit, bit 0.8.

1 = Full Duplex.

default 0 = Half Duplex.

RW

0.7

Collision Test

Force collision in response to the assertion of TXEN.

1 = Force COL.

default 0 = disable Collision signal test.

RW

0.6:0

Reserved

Constant

“

0

”

.

RO

Table 44. Status Register (Register 1) Bit Definitions

Bit(s)

Name

Description

Type

1

1.15

100BASE-T4

Constant 0 = PHY not able to perform 100BASE-T4.

RO

1.14

Reserved

Constant

“

0

”

.

RO

1.13

100BASE-TX Half

Duplex

1 = PHY able to perform half duplex 100BASE-TX

0 = PHY not able to operate in 100BASE-TX

RO

1.12

Reserved

Constant

“

0

”

.

RO

1.11

10 Mbps Half Duplex

1 = PHY able to operate at 10 Mbps in half duplex mode

0 = PHY not able to operate in 10BASE-T

RO

1.10:7

Reserved

Constant

“

0

”

.

RO

1.6

MF Preamble

Suppression

Constant 0 = PHY will not accept management frames with preamble

suppressed.

RO

1.5

Auto-Negotiation

Complete

1 = Auto-Negotiation process completed

default 0 = Auto-Negotiation process has not completed.

RO

1.4

Remote Fault

Constant 0 = no remote fault condition detected

RO

1.3

Reserved

Constant 0

RO

1.2

Link Status

1 = Valid link has been established.

default 0 = Invalid link detected.

RO

LL

SC

1.1

Jabber Detect

This bit has meaning only in 10 Mbps mode.

1 = Jabber condition detected.

default 0 = No jabber condition detected.

RO

LH

SC

1.0

Extended Capability

Constant 1 = Extended register capabilities enabled

RO

1. Refer to

Table 42

for Type definitions.

Table 43. Control Register (Register 0) Bit Definitions (Continued)

Bit(s)

Name

Description

Type

1

1. Refer to

Table 42

for Type definitions.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT970AQC | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

| LXT970ATC | Telecomm/Datacomm |

| LXT971ABC | LAN TRANSCEIVER|SINGLE|CMOS|BGA|64PIN|PLASTIC |

| LXT971ABE | LAN TRANSCEIVER|SINGLE|CMOS|BGA|64PIN|PLASTIC |

| LXT971ALC | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT980AHC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN HUB CONTROLLER |

| LXT980QC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LAN HUB CONTROLLER |

| LXT9860 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Advanced 10/100 Repeater with Intergrated Management |

| LXT9860AHC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

| LXT9860HC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Controller Miscellaneous - Datasheet Reference |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。