- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT971ALC LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | LXT971ALC |

| 英文描述: | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|單|的CMOS | QFP封裝| 64管腳|塑料 |

| 文件頁數(shù): | 45/68頁 |

| 文件大小: | 1177K |

| 代理商: | LXT971ALC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Low-Power Octal PHY

—

LXT9784

Datasheet

45

There are two NAND-Tree chains, with two separate inputs, assigned to UCA1 (Chain 1) and

COLED (chain 2), and two separate outputs, assigned to INT (Chain 1) and TOUT (Chain 2)

respectively.

To enable NAND-tree manufacturing test mode, set MODE[2:0] = "111", TCK = "0", TI = "0",

TEXEC = "1" and power-up or reset the chip. Toggling the chain input pin will be reflected at the

chain output after a delay of about 20ns.

2.12.2

XNOR-Tree Test

This command connects all the outputs of the input-buffers in the device periphery into a XNOR-

Tree scheme. All the I/O and outputs, except for MODE[2:0], TI, TEXEC, TCK, INT, and TOUT

pins, are put into a Tri-State mode.

There are two XNOR-Tree chains, with two separate inputs, assigned to UCA1 (Chain 1) and

COLED (chain 2), and two separate outputs, assigned to INT (Chain 1) and TOUT (Chain 2),

respectively.

In order to set up the device into XNOR tree manufacturing test mode set MODE[2:0] = "111",

TCK = "0", TI = "1", TEXEC = "0" and power-up or reset the chip. Toggling the chain input pin

will be reflected at the chain output after a delay of about 20 ns.

2.12.3

NAND/XNOR Tree Chain Order

A combination of

“

111

”

on the MODE_[2:0] pins indicates that the LXT9784 is configured to an

asynchronous test mode (NAND-TREE or XNOR-TREE). Test pins combinations for the

asynchronous test modes are:

MODE_[2:0] =

“

111

”

, TCK =

“

0

”

, TI=

“

0

”

, TEXEC =

”

1

”

for NAND - TREE

MODE_[2:0] =

“

111

”

, TCK =

“

0

”

, TI=

“

1

”

, TEXEC =

”

0

”

for XNOR - TREE

The NAND-TREE / XNOR-TREE commands connect all outputs of the

input-buffers

in the device

periphery into a

NAND-TREE / XNOR-TREE scheme. All the input/output pins and output pins except for:

MODE_[2.0], TI, TEXEC, TCK, INT#, and TOUT pins are put into a Tri-State mode.

There are two NAND-TREE / XNOR-TREE chains, with two separate outputs, assigned to INT#

(Chain 1) and TOUT (Chain 2).

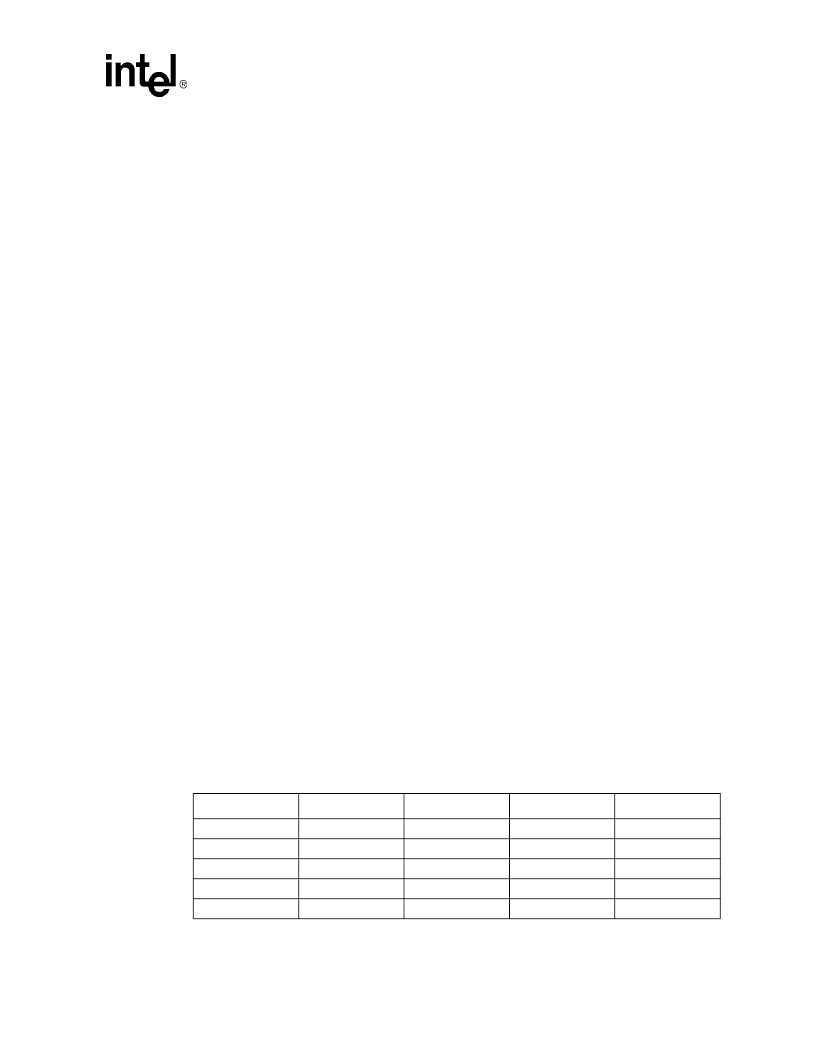

The following table lists the chains order / direction (pin no. 1 in the chain, is the farthest from the

NAND-TREE / XNOR-TREE outputs).]

Table 22. Test Scan Chain

Chain Order

Ball ID

Chain #1

Ball ID

Chain #2

1

W1

TXD0_1

W18

NC

2

W2

TXD0_1

W19

NC

3

W3

TXEN0

W20

NC

4

V1

CRSDV0

V18

NC

5

V2

RXD0_1

V19

NC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT971ALE | LAN TRANSCEIVER|SINGLE|CMOS|QFP|64PIN|PLASTIC |

| LXT974QC | LAN Transceiver |

| LXT975QC | LAN Transceiver |

| LXT9761 | Interface IC |

| LXT9761HC | LAN TRANSCEIVER|HEX|QFP|208PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT971ALE | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet PHY Transceiver |

| LXT971LC | 制造商:Intel 功能描述: |

| LXT972A | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet Transceiver Datasheet |

| LXT972ALC | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3.3V Dual-Speed Fast Ethernet Transceiver Datasheet |

| LXT972LCHFB8 | 制造商:LEVEL_ONE 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。